TSMC estaría aumentando su capacidad del encapsulamiento avanzado de chips para NVIDIA

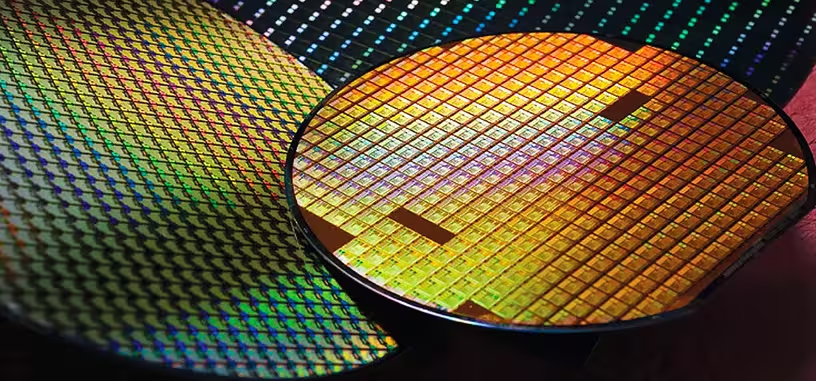

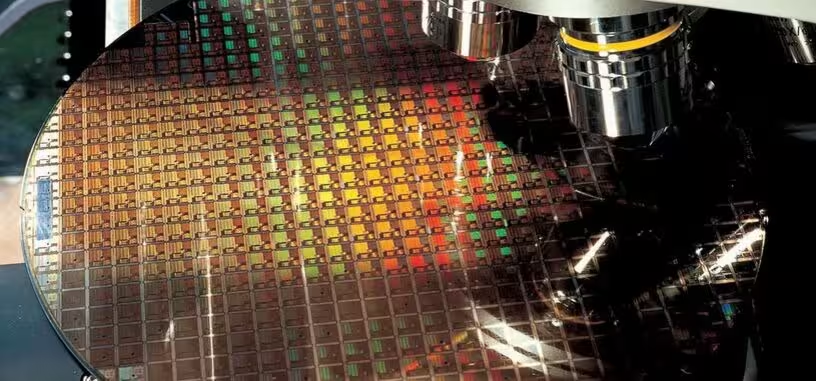

La producción de las obleas es solo una parte de la producción de los chips ya que hoy en día es tan importante o más su encapsulado. Dentro de las técnicas más solicitadas a TSMC está CoWoS (chip sobre oblea sobre sustrato), que es la utilizada para chips como los A100 y H100 de NVIDIA. Pero la altísima demanda de estas unidades de procesamiento gráfico para computación, y específicamente de inteligencia artificial, habría hecho que TSMC tenga que expandir la producción en sus plantas de encapsulado.

Sigue leyendo