TSMC es la fundición más avanzada del planeta, pero no está exenta de toparse con obstáculos a la hora de reducir sus procesos litográficos. El principal escollo actualmente es el del tamaño de la SRAM, que es la estructura básica para conformar, por ejemplo, la caché de los procesadores. Con el aumento que está habiendo en este terreno en las CPU y GPU, si TSMC no puede seguir reduciendo su tamaño llevará a chips más grandes y por tanto a mayores costes de producción.

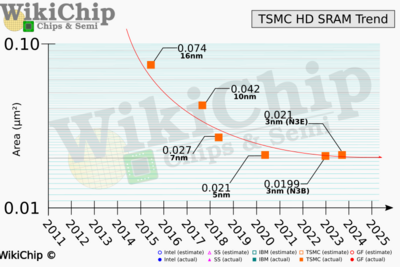

WikiChip ha hecho una análisis somero de la reducción del tamaño de estas celdas de SRAM por parte de TSMC en sus últimos procesos litográficos, mostrando que su tamaño en el proceso litográfico de 3 nm apenas se ha reducido frente al de 5 nm. Esto explicaría la decisión de AMD de llevar la caché Infinity y los controladores de memoria a chíplets distintos en la arquitectura RDNA 3 respecto al chíplet de procesamiento general: equilibrar los costes.

El diseño multichip es hacia donde va la industria salvo que TSMC sea capaz de escalar mucho mejor la SRAM o maduren formas alternativas de crear caché, como MRAM, FeRAM y similares, que puedan reducir más su tamaño frente a la SRAM. De lo contrario, crear chips monolíticos llevará a un aumento del porcentaje que ocupa la SRAM en los chips, produciéndose menos chips por oblea, y por tanto aumentando su precio en las litografías más avanzadas.

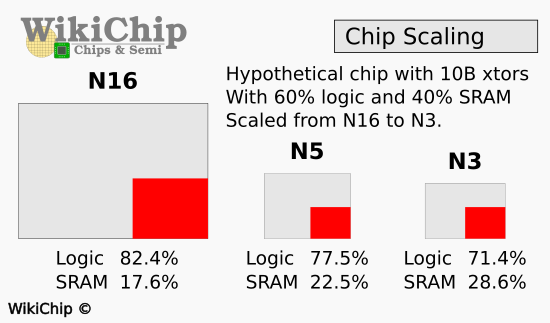

En la imagen de más abajo se ve aún mejor el problema. Los chips que está produciendo TSMC a 3 nm podrían ser bastante menores si hubiera conseguido reducir más, o algo, el tamaño de la SRAM. Esta SRAM de un mismo chip diseñado a 5 nm y a 3 nm ocupa un 22.5 % y un 28.6 % del área del chip, respectivamente. Es cuanto menos curioso que en el proceso de 16 nm ocuparía solo el 17.6 % del área.

La construcción de las celdas de SRAM se hace principalmente con una estructura de varios transistores unidos y es más complicado de mantener su estabilidad de funcionamiento. Como he dicho, la caché (SRAM) es cada vez más importante para aumentar el rendimiento de los procesadores. Por ejemplo, NVIDIA ha multiplicado por dieciséis la cantidad de caché de nivel 2 en la arquitectura Ada, lo que explica también por qué el chip AD102 no es más pequeño pese al gran salto en la litografía, desde los 8 nm de Samsung a los 4 nm de TSMC.

Fuente: WikiChip. Vía: Tom's Hardware.