ASML es el mayor fabricante de maquinaria litográfica y está actualmente muy por delante de su competencia, a años luz. Sabe que si compañías como TSMC, Samsung o Intel pueden desarrollar chips pensando en procesos litográficos de 5 nm, 3 nm o incluso menos en los próximos años es gracias a las máquinas que construye. Eso hace que tenga una especial relevancia lo que dice sobre el futuro cercano en procesos litográficos porque es la que establece lo que va a ocurrir. De ahí una interesante predicción de que para 2030 se podrán crear procesadores que incluyan hasta 300 000 millones de transistores.

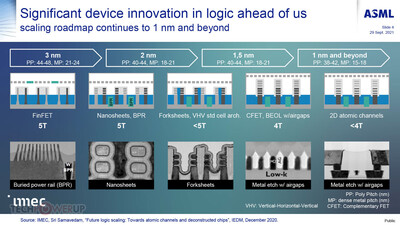

En la actualidad, chips avanzados como el incluido en el M1 de Apple que está fabricado a 5 nm tiene 16 000 millones de transistores. De ahí hasta los 300 000 millones que augura ASML hay mucho camino que recorrer, aunque lo ve viable con diferentes cambios de estrategias en el diseño de los transistores. Actualmente se usa mayoritariamente la estructura FinFET en los procesos litográficos avanzados, pero pronto se usarán los GAAFET en diversas variantes según el desarrollador del proceso litográfico. Las máquinas de ASML lo permitirán o de otra forma ni Samsung, ni Intel ni TSMC podrían cumplir con sus objetivos.

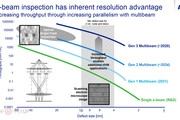

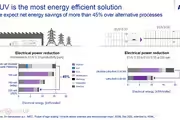

El tema central de la charla de ASML en su Día de Inversores, cuyas diapositivas tenéis más abajo, es sustentar el avance de la ley de Moore que según la compañía está bien viva y lo seguirá estando. Principalmente se conseguirá usando la nueva generación de escáneres litográficos que usará una alta apertura numérica (HNA) que tiene todavía en desarrollo. La apertura numérica es un valor que determina el ancho del haz que se emite contra la oblea. A mayor amplitud mayor intensidad del haz y más fácilmente se puede transferir el diseño de un fotolito a una oblea. Estarán listos previsiblemente para 2024.

Eso habilitará nuevas estructuras de transistores más complejas de aquí a 2030 para conseguir ese objetivo de reducir su tamaño para que haya 300 000 M en un solo procesador o sistema en chip. A continuación relata hacia dónde se dirige el sector en estructuras de los transistores de efecto de campo (FET), que son algunas cosas bastante recientes pero no salen expresamente de ASML sino de las universidades y empresa que están investigando sobre ello.

El paso a GAAFET (transistor de efecto de campo de puerta amplia) implica que el canal de transmisión son nanoláminas o nanotubos rodeados de un material que hace de puerta y por tanto hay más superficie de contacto con más paso de corriente. De esa estructura se pasará a los FET de láminas divididas (FFET) en los 2 nm, que divide las uniones N (nFET) y P (pFET) del transistor y las separa con un material o muro dieléctrico. La ventaja es que son la misma estructura para ambas uniones en lugar de ser estructuras diferenciadas reduciendo lo que ocupan. Esta estructura se propuso en 2019, por lo que entenderéis que es tecnología en estado teórico. De ahí hay que llevarlo a lo práctico.

El siguiente paso será a los CFET (FET complementario) y modificar los BEOL (contactos terminales de línea) incluyendo separaciones de aire, en el que se vuelve a dar el paso de apilar la estructura anterior. O sea, en lugar de tener las uniones PN separadas en horizontal se pasan a apilar en vertical, o técnicamente «doblar» el nFET sobre el pFET, nuevamente ganando espacio. BEOL hace referencia a la parte más inferior de la creación de los transistores —que en realidad es la parte más cercana a la superficie de la oblea porque luego los chips se cortan y voltean para empaquetarlos—, las interconexiones con el resto del chip, donde habrá que hacer cambios mayúsculos para que se comuniquen adecuadamente. Os habréis dado cuenta de que incide mucho la compañía en ganar espacio para llegar a su objetivo. Este tipo de transistores se usaría para la litografía de 1.5 nm, o 15 Å como la llamaría Intel.

De ahí, el futuro es más incierto. Pasado el nanómetro (1 nm) de tamaño de los transistores se llegan a estructuras atómicas 2D para el canal de los transistores sin que haya ninguna estructura adicional salvo por las reestructuraciones de CFET, las capas metálicas de la oblea, más espacios de aire entre transistores, etc. Con ello se conseguirán esos 300 000 millones de transistores en un solo procesador en 2030 manteniendo la ley de Moore, aunque eso no evita que se sigan desarrollando tecnologías de oblea sobre oblea, chip sobre silicio sobre sustrato (CoWoS), etc., para apilar chips.

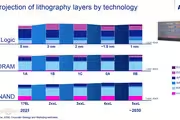

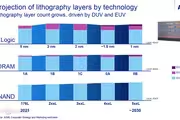

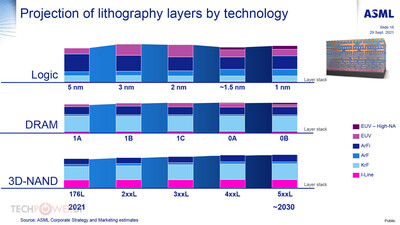

También hace un repaso al número de capas de memoria NAND 3D que se pueden crear con la maquinaria actual y cuánto se va a necesitar la de luz ultravioleta extrema (UVE) que produce la compañía. Ahora mismo se usa mayormente en un puñado de capas de DRAM aunque en NAND 3D no se van a necesitar de momento. En esos sectores se utilizan para la mayoría de las capas unos escáneres de luz ultravioleta profunda (UVP) con láseres de fluoruro de argón (ArF) o su variante de inmersión (ArFi) en que la separación entre luz y oblea no está lleno de aire sino de un líquido. Específicamente, en la NAND 3D no se necesitará hasta después de 2030 la maquinaria de luz ultravioleta extrema, y en la DRAM solo se precisará la extrema de alta AN en unas pocas capas para mantener la reducción de estos chips.

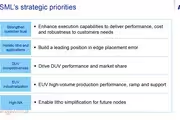

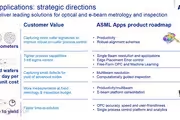

Tras el repaso a por dónde va a ir el sector de los semiconductores en los próximos años entra a analizar las estrategias de la propia compañía. Entre ellas, cómo no, la de saber qué es importante para el cliente y qué puede ofrecer ASML para proporcionárselo: metrología, inspección y control de patrones. Hace referencia al escáner TWINSCAN NXT:2050i de luz ultravioleta profunda que se usa en procesos litográficos por debajo de los 5 nm. No todas las capas de una oblea se producen luz UVE sino solo una pequeña pero creciente cantidad a medida que se van a litografía menores.

Hay que tener en cuenta que estas máquinas litográficas no se compran, se envían al comprador, las pone en alguna parte de una fábrica y ya está. Se tienen que construir casi literalmente en las instalaciones por lo que requiere bastantes ingenieros, técnicos y tiempo (días a semanas) para instalarlas donde diga el cliente, más el periodo de pruebas de que se ha instalado correctamente, y otro periodo de pruebas por parte de la fundición de chips para probar sus procesos litográficos. Puede llevar meses la puesta en marcha de una de estas máquinas, sobre todo en las de luz UVE, y especialmente las que prepara de alta apertura numérica.

Una máquina de UVP es pequeñita en comparación con una de UVE de HNA que puede tener unos 12 m × 5 m × 5 m, incluso más porque la compañía está finalizando el desarrollo de estas máquinas. Son las máquinas que se necesitarán en las capas más avanzadas de una oblea para poder llegar a los 2 nm. También permitirán la eliminación de más capas hechas con patrones múltiples, reduciendo tiempos de producción y complejidad del proceso en general. Lo que busca ASML en las nuevas máquinas de alta AN es reducir el tiempo de puesta en servicio, aumentar la cantidad de obleas procesadas cada día y reducir los tiempos de espera en los procesos del cliente —comprobación de capas, monitorización de defectos, etc.—.

Lo que trata ASML en estas transparencias en realidad va mucho más allá de lo que se suelen tratar en los medios generalistas de tecnología ya que precisa de ciertos conocimientos de procesos litográficos que no tiene la mayoría de editores, pero en este caso para mí no son cosas nuevas. Os recomiendo echar un vistazo a las transparencias y si tenéis alguna duda ya sabéis dónde están los comentarios.

Vía: TechPowerUp.