Algunos fabricantes de chips de memoria llevan tiempo trabajando en el procesamiento en memoria (PIM) que consiste en dotar a los chips de memoria de cierta capacidad de procesamiento de la información que mueven para agilizar ciertas cargas de trabajo. Tanto Samsung como SK Hynix han estado trabajando en ello, pero ha sido la primera la que ha hablado extensamente de ello en el Hot Chips de este año.

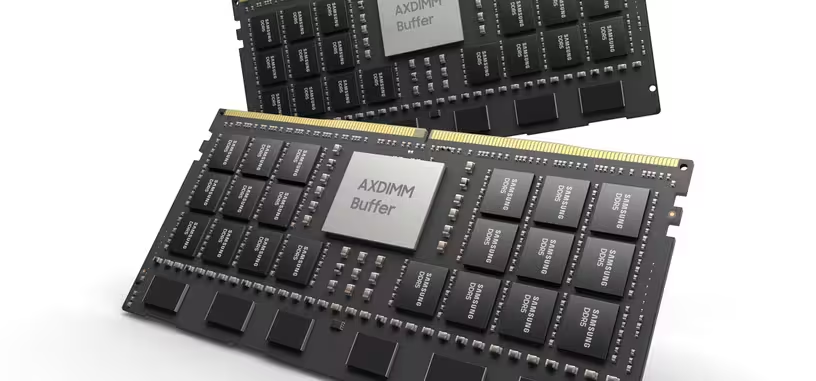

Estas soluciones están orientadas a inteligencia artificial y por ahora se han centrado en la memoria de alto ancho de banda (HBM) conformando lo que se conoce como HBM-PIM. Lo siguiente es combinarla con DDR5 creando módulos con PIM. El resultado lo tenéis a continuación, ya que Samsung ha distribuido una nota de prensa haciendo referencia a ello fuera del Hot Chips.

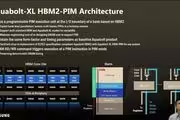

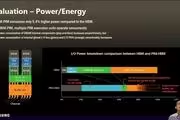

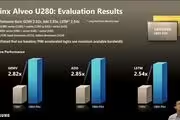

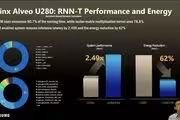

La primera parte de la nota es la HBM-PIM de tipo Aquabolt-XL con la aceleradora Alveo de Xilinx con lo que consiguen un rendimiento mejorado un 150 % con una reducción del consumo del 60 %. Esa es realmente la ventaja del procesamiento en memoria. La segunda parte ha cubierto los módulos DDR5 con PIM, cuyas imágenes tenéis a continuación.

Son DIMM normales para pinchar en un equipo cualquiera; no necesita configuración especial en el equipo para reconocer estos AXDIMM (DIMM de aceleración). El módulo incluye varias filas de memoria en lugar de solo una para aumentar el acceso paralelo, potenciado por un chip de búfer y procesamiento. El resultado es una reducción del 40 % en el consumo en cargas de trabajo sencillas en las que se pueda usar el procesamiento de ese chip adicional. Habrá versiones de LPDDR5-PIM para dispositivos de bajo consumo (portátiles, mini-PC), pero también habrá DDR4-PIM.

Dejando atrás la nota de prensa, que siempre se centra en generalidades, en el Hot Chips 33 la compañía ha dado los detalles técnicos específicos de su DDR5-PIM, DDR4-PIM, LPDDR5-DIM, HBM2-PIM, HBM3-PIM y demás módulos que tiene en desarrollo con procesamiento en memoria. Lo importante de los chips con PIM es que usan la interfaz estándar del controlador de memoria por lo que las soluciones de memoria actuales solo precisarían de cambiar los chips no PIM por los PIM para empezar a funcionar.

Por ahora solo puede procesar ciertas instrucciones básicas, FP16 en la HBM2, pero pretende mejorarlo a FP64 en HBM3, y en el caso de la DDR5 y GDDR6 con PIM usarán otras instrucciones para INT8, INT16 o FP32, por ejemplo. La cuestión será adaptar las capacidades de procesamiento, sin añadir una excesiva complejidad (y consumo) al procesador integrado en memoria, a las necesidades de cada tipo de memoria y casos de uso en los centros de datos.

Entrando en el funcionamiento del PIM, lo que se pretende en realidad es aumentar el ancho de banda de memoria efectiva eliminando movimiento innecesario de información entre la CPU del equipo y los módulos de memoria. Si puedes ejecutar una serie de cálculos FP16 en la memoria será bastante más eficiente que si tienes que llevar la información de la memoria a la CPU, realizar allí los cálculos y devolverlo a la memoria. En ese sentido Samsung menciona que el ancho de banda al final está limitado por el número de contactos del encapsulado de los chips de memoria, limitaciones térmicas, conexiones, canales, etc.

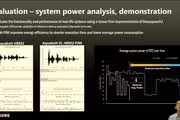

En alguna de las transparencias de abajo se indica la estructura de la PIM, tanto el controlador como los registros que incluye o las operaciones que puede realizar. Aunque los módulos son de pinchar y usar, para aprovechar el procesamiento se precisará de una pila de software específico a implementar en el sistema. Es compatible con bibliotecas de inteligencia artificial como TensorFlow o Pytorch, lo cual permite dos modos de funcionamiento: ejecución nativa, en el que se descargan ciertos tipos de operaciones al chip del PIM sin tocar el código del programa de cómputo que se esté ejecutando; y ejecución directa, que permite decidir qué y cómo se ejecuta en el chip del PIM.

El resultado es que la HBM con PIM consume solo un 5.4 % más de energía pero a cambio permite aumentar hasta diez veces el rendimiento en ejecución de ciertas cargas de trabajo reduciendo el consumo de transferencia de bits entre CPU y HBM hasta un 70 %, reduciendo además el tiempo de procesamiento de esos datos.

Fuente: Samsung. Vía: Tom's Hardware, AnandTech.