Como parte del Día de Arquitectura 2021, Intel ha dado más detalles del futuro de sus procesadores Xeon para los centros de datos. Los actuales, bueno, se están vendiendo debido a que los proyectos en curso los necesitan en mayor o menor medida, pero AMD y sus EPYC están acaparando rápidamente cuota de mercado de los nuevos proyectos. Está por ver si la arquitectura Sapphire Rapids es tan buena como ha prometido Intel y ha reiterado en estas jornadas.

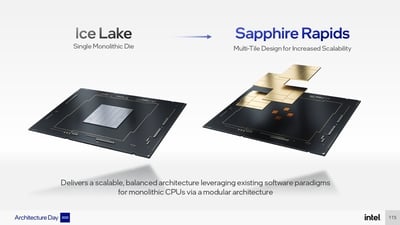

Esta arquitectura realiza mejoras al procesador, el zócalo y el propio centro de datos para ofrecer mejores herramientas de telemetría, calidad de servicio (QoS) o virtualización. Pero más allá de hablar de ello muy de pasada, la compañía se ha centrado en hablar de los procesadores en sí, los chíplets que lo componen y su encapsulado. Una buena parte de sus características ya habían sido compartidas, pero Intel va al detalle de los chíplets o teselas (tiles) como las llama porque considera a sus procesadores multichips como mosaicos compuestos por teselas.

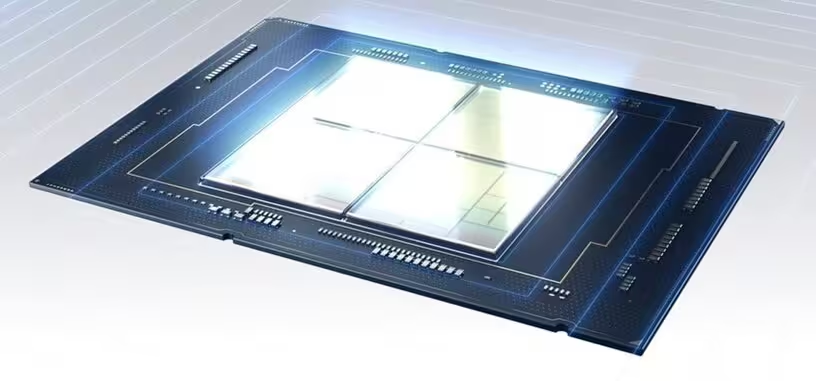

Estos chíplets están fabricados con el proceso 7 de Intel, el anteriormente conocido como 10 nm SuperFin mejorado. Cada procesador Sapphire Rapids puede contener hasta cuatro chíplets conectados a su vez externamente mediante una interconexión de alta velocidad y baja latencia haciendo que parezca un procesador monolítico ya que todos los chíplets tienen acceso a los recursos ubicados en cualquiera de ellos. Es probable que sea el motivo por el que Intel las llame teselas y no chíplets porque generalmente este último término hace referencia a un chip que solo tiene una parte de la funcionalidad del conjunto y en este caso cada tesela es un sistema completo.

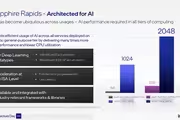

Ciertos modelos de estos Xeon irán encapsulados junto a memoria de alto ancho de banda (HBM) ya que proporcionará más ancho de banda que DDR5 y para ciertos tipos de carga, sobre todo de inteligencia artificial, es conveniente tener el mayor posible. Además, reduce la latencia al estar encapsulado junto al procesador y reduce sustancialmente su consumo. Pero que integren HBM no significa que dejen de usar DDR5, sino que la integrará además de la DDR5. La HBM podrá funcionar de manera conjunta o como caché de la DDR5.

Cada chíplet lleva un controlador de memoria y la DDR5 se podrá usar en modo ocho canales. Junto con los más de 100 MB de caché de último nivel que puede integrar un Sapphire Rapids y la memoria persistente Optane de nueva generación, la memoria no parece que vaya a ser un problema de estos procesadores. Tendrán acceso a prácticamente toda la que quiera el que monte el servidor.

Los núcleos están conectados en malla, todos con todos, y a través de la interconexión con otros chíplets. La conexión PCIe incluida es la versión 5.0, que da sustento a CXL 1.1 (enlace exprés de cómputo), el protocolo de conexión externa desarrollada por Intel y a la que se ha sumado todo el sector, hasta AMD, por las ventajas que proporciona de eficiencia, latencia, y los distintos modos de uso.

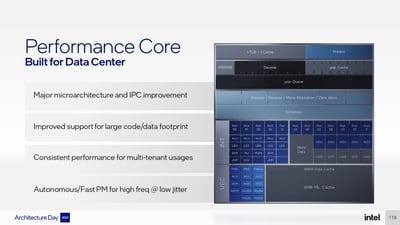

Sobre la arquitectura de los núcleos no ha comentado gran cosa aunque habrá cambiados en todos los frentes por la nueva generación de la arquitectura, en la línea de lo proporcionado en los Alder Lake y el núcleo P. Son en realidad bastante distintos porque incluyen ciertas características orientadas al cálculo de inteligencia artificial y el aprendizaje automático, como un conjunto de instrucciones de matrices (tensores) para inferencias y entrenamiento de redes neuronales llamado AMX (extensiones matriciales avanzadas), o implementación de cálculos en coma flotante en precisión simple (FP16). No es lo ideal que se haga en una unidad central de procesamiento, pero no molesta ya que será de utilidad en algunos microservicios, que es el otro sector al que van orientados estos procesadores y un terreno en el que también destacarán.

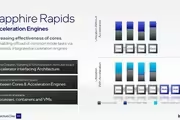

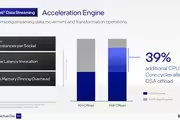

Los núcleos van acompañados de unos motores de aceleración, que es como se llaman, de estas cargas de trabajo con los que se ganará hasta un 39 % más de procesamiento de datos en un momento dado, reduciendo enormemente el movimiento de datos propiamente dicho.

Permiten descargarles tareas como compresión y descompresión a una velocidad de hasta 160 Gb/s, realización de cifrado simétrico a 400 Gb/s, o ejecución de operaciones (instrucciones) fusionadas —realiza varias operaciones sobre los datos realimentando el resultado, por ejemplo al calcular un sumatorio— como las de tensores —frente a las operaciones primitivas, como una simple suma—. Eso lleva al grandilocuente dato de que si se descargan esos trabajos a los motores de aceleración el núcleo en sí solo se queda cargado al 2 % por lo que el 98 % restante se puede usar para otros propósitos.

Los procesadores Sapphire Rapids estarán en producción en el primer trimestre de 2022 y en masa en el segundo trimestre de 2022.