Samsung ha llegado al Hot Chips 2021 en su tradicional cita del verano boreal dando detalles de sus avances en el terreno de la memoria DDR5. Aunque el sector está dando sus primeros pasos, a finales de año cobrará fuerza con la llegada de los primeros procesadores de Intel compatibles con ella. Después de ello llegará a los centros de datos donde necesitan una alta capacidad por ranura de memoria. Por eso para ese sector la compañía prepara módulos de 512 GB.

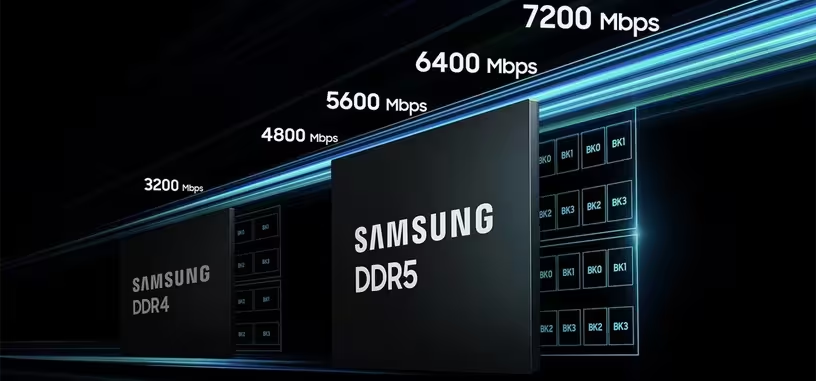

La compañía habla de una velocidad de 7200 Mb/s (o MHz) para estos módulos (RDIMM/LRDIMM, no UDIMM de consumo) alejándose lo suficiente de los 4800 Mb/s base del estándar de la JEDEC. No ha dado detalles sobre las latencia de funcionamiento, pero en los centros de datos suele ser algo más secundario aunque también importe. Podrían ser de hasta 60-60-60 aunque la JEDEC de momento solo tiene especificados los 6400 MHz con perfiles de 46-46-46 y 56-56-56.

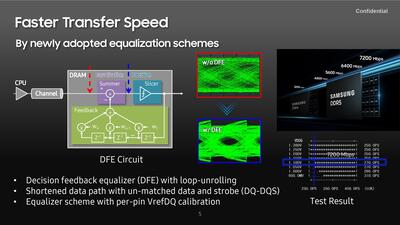

El aumento de la memoria precisa de una mayor estabilidad en la transmisión de la señal y en este caso se consigue aumentar con un ecualizador con realimentación de decisión (DFE), entendiendo al ecualizador en su sentido genérico de ajustar la señal de la memoria entre unos valores determinados por Samsung para estos módulos.

El circuito de realimentación introduce una corrección al símbolo de entrada (un bit, por ejemplo) en base a los previos de una manera no lineal para no añadir ruido intersímbolo. Como todos los sistemas no lineales, los DFE son circuitos mucho más complejos de diseñar y por tanto caros. Lo que se pretende con ello es crear un diagrama de ojos mucho más definido lo que es síntoma de menor ruido en línea. Pero estos cambios son para aumentar la frecuencia, y queda el tema de la capacidad que es igual de importante.

Para llegar a esa capacidad de 512 GB la compañía ha desarrollado un nuevo sistema de creación de vías a través de silicio (TSV) que unen las distintas capas apiladas de memoria DDR5. Por un lado la compañía ha reducido la separación entre capas —chips en bruto— un 40 % pero también el grosor de las obleas lo que permite crear chips de ocho capas de memoria en una altura un 20 % que la de la memoria DDR4. También incluye una serie de mejoras a nivel de impedancia para favorecer la refrigeración de los chips, aunque no ha dado datos concretos de temperaturas de funcionamiento.

Por último, lo que está permitiendo alcanzar una alta velocidad y capacidad en estos módulos es que el chip de gestión de energía (PMIC) está integrado en ellos en lugar de en las placas base. Esto permite regular el voltaje mucho más cerca de los chips de memoria lo que lleva a menos ruido y por tanto frecuencias mayores. Por tanto el diseño del PMIC debe ser mejor en módulos de alta frecuencia, que en este caso siguen funcionando a 1.1 V con un proceso de puerta metálica de alta K (constante dielétrica) que es la primera vez que se usa en la DRAM siendo más propio de la fabricación de procesadores.

Pero además de esta gestión de voltajes la forma de evitar errores es con código de corrección de errores (ECC) integrado en el chip, que a pesar de que no es tan fiable como el externo la compañía ha asegurado que se mejora la tasa de errores de bit a 10–6. De hecho el ECC siempre ha sido una forma de asegurar mayores frecuencias de funcionamiento que por alguna razón nunca llegó al sector generalista y se quedó en el sector de los prosumidores y profesionales.

Los primeros módulos de DDR5 de 512 GB entrarán en producción a finales de año, listos para el lanzamiento de los primeros procesadores para centros de datos compatibles con DDR5.

Vía: AnandTech.