TSMC sigue liderando el sector de la producción de semiconductores con sus litografías, y teniendo en cuenta que los primeros chips fabricados a 2 nm (N2) están al caer, el siguiente paso será será el de 1.6 nm (A16), y una evolución en forma del proceso de 1.4 nm (A14). La compañía ha hablado de este proceso litográfico indicando que será un salto generacional, por lo que no será una versión mejorada del de 2 nm. Eso significa que promete mejoras sustanciales, aunque quizás no tanto como muchos esperarían.

Según su vicepresidente sénior de desarrollo de negocio, Kevin Zhang, la mejora que aportará el de 1.4 nm frente al de 2 nm será de 25-30 % menos de consumo a mismo rendimiento, un 10-15 % más de rendimiento a mismo consumo, con una mejora del 23 % de la densidad de los bloques lógicos del chip, o un 20 % en diseños mixtos. Eso implica que habrá mejoras tanto en los bloques lógicos del chip como en los de SRAM, que en la última década su densidad ha bajado poco.

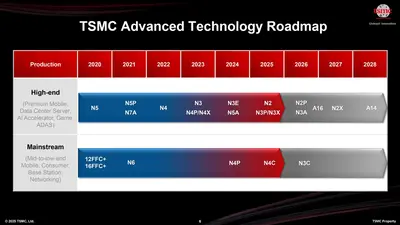

Ha asegurado que la compañía lleva el desarrollo de este nodo muy bien, y que ya tiene una productividad mayor de la esperada en su fase actual. Si el proceso va a estar ampliamente disponible en 2028, eso significa que desde 2027, en un par de años, se usará en producción en masa.

El proceso hará uso de los GAAFET de segunda generación que ha desarrollado la compañía, con mejoras en la capacidad de ajustar la corriente que pasa a los transistores. Pero va a eliminar en este diseño la entrega de energía en la trasera del chip, por lo que estará orientado a otro tipo de chips en los que este sistema de distribución de la energía no aporta beneficios. O sea, aquellos en los que la estabilidad de la señal no sea tan problemático porque no alcancen muy altas frecuencias.

Con esta litografía debutará la tecnología NanoFlex Pro de TSMC, una metodología basada en la cooptimización de tecnología de diseño (DTCO) que permite una selección más fina de ciertos aspectos del diseño de un chip en función de sus necesidades reales. Por ejemplo, mezclar en un nuevo bloque lógico partes de bloques lógicos orientados a alto rendimiento con los de bajo consumo. Lo tienen ya integrado empesas como Synopsys en sus programas de diseño, por lo que actualizarlo a NanoFlex Pro será poco trabajo y realmente útil. La primera versión está diseñada para chips sin la entrega trasera de energía, así que por eso debuta con el A14 y no con el A16 que sí la tiene.

Vía: Tom's Hardware.