TSMC no había hablado hasta ahora demasiado de su nodo litográfico de 2 nm (N2) el cual será el primero que usará un nuevo tipo de transistores que dejará atrás los FinFET. En este caso usará los GAAFET (transistor de efecto de campo de puerta envolvente) en el que el canal pasa a ser nanoláminas apiladas y la puerta envuelve totalmente a estas nanoláminas. Tiene ventajas de reducción de energía necesaria para hacer funcionar los transistores o menos corriente de fuga, entre otros. Ahora la compañía ha dado datos de la mejora que aportará este nodo N2.

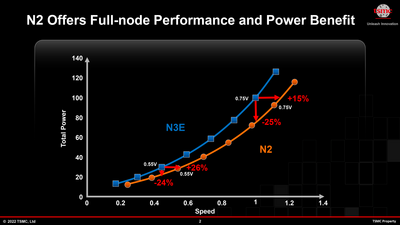

El salto está en la línea de lo que se ha venido consiguiendo en cada generación. Frente al N3E, el proceso N2 aportará hasta un 30 % menos de consumo a misma frecuencia o hasta un 15 % más de rendimiento a mismo consumo. Es similar a lo experimentado en el saltado del N5 al N3. Sin embargo, TSMC solo habla de una mejora del 10 % en la densidad de los transistores, que es un poco chocante debido al uso de los GAAFET y realmente sabe a poco.

Me imagino que cuando entre a hablar a fondo de su itinerario con el N2 y procesos derivados ofrecerá varios tipos optimizados y que habrá mayores mejoras en el terreno de la densidad a coste del consumo o el rendimiento, pero en un diseño estándar no parece que vaya a haber una gran reducción en el tamaño de los chips. El proceso litográfico N2 entrará en producción en masa en 2025 si no pasa nada extraño. Quizás incluso antes porque en el terreno del I+D la compañía ha estado por delante de lo previsto para el N3.

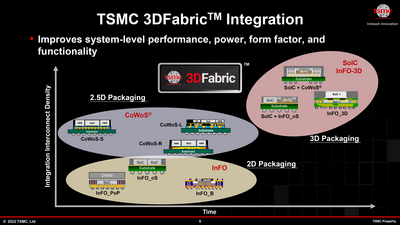

Esos procesos optimizados se conseguirán gracias a que controlando el ancho de las nanoláminas se puede aumentar la potencia del chip haciéndolas más anchas o reducir su consumo haciéndolas más estrechas. Eso proporcionará una gran flexibilidad en las variantes de procesos litográficos que ofrezca la compañía. También se incluirá una cierta oferta de adaptación a distintos tipos de encapsulamientos, incluidos la de crear chíplets para módulos multichip. Teniendo en cuenta el consorcio UCIe, es normal que empiece a tenerlo en cuenta.

Vía: AnandTech.