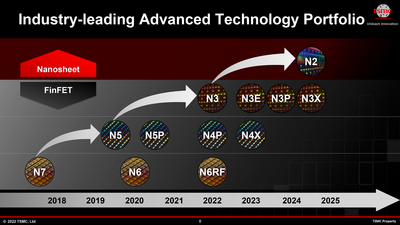

TSMC ha dado poca información sobre su proceso litográfico de 3 nm hasta el momento, aunque tampoco es que fuera a haber grandes cambios. La compañía va a mantener la estructura de aleta de los transistores (FinFET), que recibe el nombre por la forma en que sobresale la región de los terminales de puerta y drenador de los transistores sobre la superficie en que se crean —por lo que también se les llama transistores 3D—. Ahora la compañía ha hablado más del proceso de 3 nm, o más bien de la familia de procesador de tres nanómetros, o N3 en la jerga de la compañía.

Van a ser cinco procesos litográficos N3 los que ponga TSMC a disposición de sus clientes, siendo los dos primeros los tradicionales N3 y N3E para 2022 y 2023, el proceso litográfico inicial y el mejorado, a los que se suma otros tres englobados en lo que llama FinFlex, que significa «aleta flexible» porque pueden variar el tamaño del canal en función de las necesidades de sus clientes. Esos procesos son los N3P, N3S y N3X en función de si se pone el foco en mejorar el rendimiento, la densidad de transistores o el consumo. Estos estarán disponibles en algún momento de 2024.

Es habitual que los fabricantes de chips ofrezcan distintas versiones de su proceso litográfico para que el cliente elija qué quiere primar en sus chips. En el caso de Intel, su proceso de 4 nm no tendrá esta posibilidad porque entiende que desarrolla un proceso que vale para todo. En el caso de TSMC, va a seguir la misma senda hasta ahora, aunque más optimizada y haciéndola un poco más pública. Es habitual que los diseñadores de chips contacten con las fundiciones pidiendo un proceso con mayor densidad, consumo o potencia, y es a lo que se refieren NVIDIA o Apple cuando hablan de que sus chips están fabricados con «procesos litográficos a medida».

En el caso que me ocupa, el motivo principal es que en lugar de poner un proceso litográfico mayor en el mercado cada dos años, con el N3 (y sus derivados) aguantará dos años y medio y con el N2 (2 nm) aguantará tres años. Eso significa que más allá del N2, que llegará en 2025, su sucesor no estaría listo hasta 2028. Obviamente la compañía ofrecerá cuando sea oportuno, en 2025 me imagino, una actualización a su itinerario de procesos litográficos.

Volviendo al proceso N3, la compañía promete un 34 % menos de consumo frente al N5 a misma frecuencia, un 18 % más de rendimiento a mismo consumo, o una reducción del espacio ocupado de estructuras lógicas equivalentes entre ambos procesos del 37.5 % con un aumento del 60 % en la densidad de transistores por milímetro cuadrado. Al final será una combinación de esos parámetros a petición del cliente.

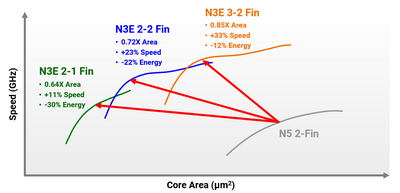

El proceso litográfico N3E entrará en producción de prueba en las próximas semanas. También ha querido hablar la compañía de FinFlex, la manera en que permitirá a sus clientes una personalización mucho más granular de los chips para que encajen totalmente con sus requisitos de consumo-densidad-potencia. Esto permite varias configuraciones de su proceso N3E en función de qué quiere optimizar el cliente en su chip, según lo indicado en la siguiente transparencia.

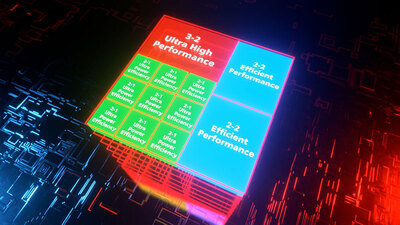

Habrá un catálogo variado de estructuras con las que crear los chips con ese objetivo. Por ejemplo, si el cliente quiere el máximo rendimiento, tendrá sus estructuras lógicas con tres puertas y dos aletas para crear los chips que darán hasta un 33 % más de frecuencias con un ahorro de solo un 12 % y una reducción de área de solo el 15 %. Sin embargo, si quiere minimizar el consumo, podrá crear los chips con estructuras de transistores de dos puertas y una aleta obteniendo un 30 % menos de consumo con una reducción de área del 36 % y un 11 % más de velocidad, siempre referido al proceso de 5 nanómetros que usa simplemente dos aletas por puerta.

Además, a diferencia de procesos litográficos anteriores, se pueden mezclar las estructuras de cada combinación de transistores dentro del mismo bloque implementado. Por ejemplo, se puede usar una estructura 3-2 para la CPU de alto rendimiento y una 2-1 para un bloque tipo GPU de bajo consumo, lo cual es ideal para los diseñadores de chips. De otra forma tendrían que aplicar una u otra. No sustituirá a los procesos específicos que priman el rendimiento, consumo o área, pero al poder mezclarlos en un mismo chip proporciona una gran flexibilidad de diseño.

Vía: AnandTech.