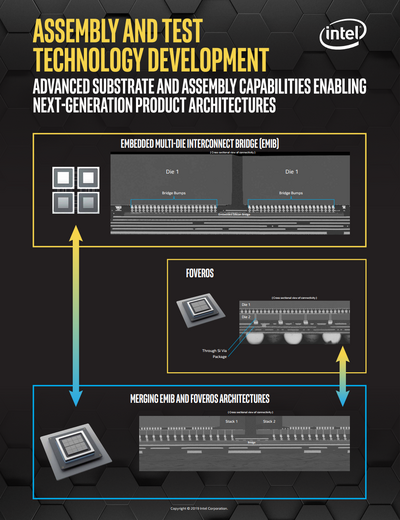

Los desarrolladores de procesos litográficos están tanteando otras tecnologías de producción de chips que vayan más allá del habitual proceso de crear una oblea, de ahí extraer los chips en bruto (pastillas) y empaquetarlas en otra instalación. Intel tiene bastante avanzadas otras tecnologías de empaquetamiento, como son Foveros, que permite el apilamiento de varios chips en un solo chip, y EMIB, que son las siglas de puente de interconexión multichip y que, como el nombre indica, permite conectar varios chips en un solo paquete.

Ahora la compañía ha anunciado Co-EMIB, que es un proceso bastante más complejo y que mezcla Fovero y EMIB, pero al que añaden una salsa McDonald's —me acabo de zampar una Big Mac (publicidad gratis)— en forma de la nueva interconexión llamada ODI (interconexión omnidireccional).

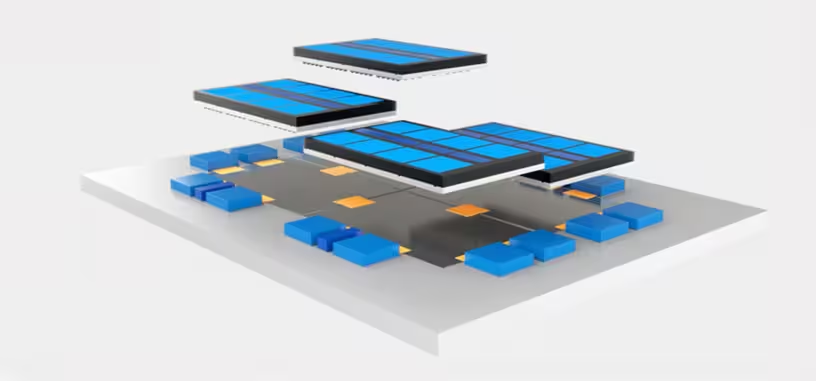

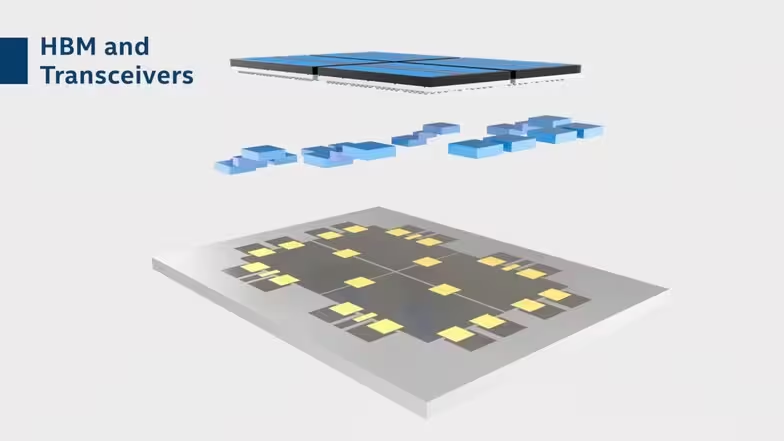

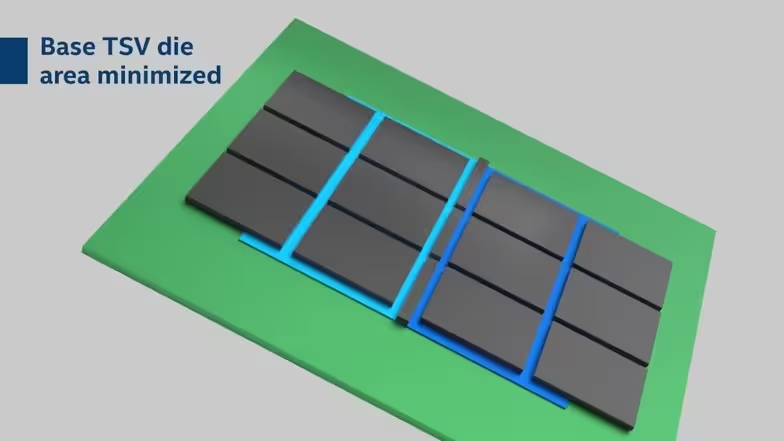

En un vídeo explica en qué consiste, y me parece bastante instructivo. Ahí se puede ver que usan Foveros para hacer el apilamiento de chips directamente en la oblea (chip sobre oblea), con la creación de las vías a través de silicio y las zonas de contacto para crear un encapsulado unitario de varios chips —que es donde meten EMIB— y llevarlo al paquete con otros módulos similares y otros chips.

Es un proceso que debe ser endiabladamente complejo en el plano de la producción de las obleas porque aumenta el número de pasos —cambios de máquina, básicamente— que se tienen que dar en el proceso de cada oblea. La introducción de ODI es necesario para conectar los chips ya que se trata de una interconexión de baja latencia entre pastillas, y que este empaquetamiento permite que los chips reciban la alimentación directamente del paquete en lugar de a través de otras conexiones.

La compañía no ha dado datos de qué entiende por «baja latencia», pero es de esperar que dé más detalles en los próximos meses. Quizás en el Hot Chips de agosto, que es la cita estrella anual del mundo de los semiconductores.

Por último, la compañía también ha indicado el uso de la interfaz de comunicación entre pastillas llamada MDIO, que no indica qué significa pero sí que es nueva, si bien coincide en nombre con el MDIO de gestión a nivel físico de Ethernet (management data input/output, gestión de datos de entrada/salida). Tiene mejor eficiencia energética, y se basa en AIB (interfaz de bus avanzado), y duplica la velocidad por pin y el ancho de banda ofrecido por AIB. Aporta una serie de bloques de desarrollo de chips para simplificar su creación.

Todas estas tecnologías para la creación de chips avanzados sobre el papel pintan muy bien, pero son tecnologías que al final al consumidor no le van a afectar demasiado. Están pensadas para crear chips para servidores y comunicaciones, entre otros, de bajo consumo y alto rendimiento, pero sobre todo muy flexibles a la hora de configurarlos. Su coste puede ser mayor o menor, dependiendo del rendimiento de producción —chip sobre oblea es por lo general más caro que otros métodos que se están desarrollando de oblea sobre oblea—.