AMD se ha adelantado a Intel en lo referente a llevar los chíplets al sector de los procesadores de sobremesa, si bien Intel ya lo tenía en uso en su FPGA llamada Stratix 10 TX. Chíplet es un derivado de chip y hace referencia a una forma de crear procesadores basada en su subdivisión en bloques lógicos que cada uno es un chip independiente, y que posteriormente se interconectan a través de un intermediador o interfaz eléctrica de unión. En lugar de un procesador de diseño monolítico, el chip se diseña de manera modular. En el futuro cercano, y sin demasiadas sorpresas, Intel va a implementar este diseño con chíplets en algunos de sus procesadores.

Lo ha anunciado junto con el nombre de la tecnología, Foveros. Con ella pone en práctica diversas tecnologías que ha estado usando en los últimos tiempos para sus procesadores, como por ejemplo mezclar chips creados con distintas litografías en un mismo encapsulado —los procesadores Kaby Lake G con chip gráfico dedicado Radeon Vega y chips HBM2—. La presentación de esta tecnología ha corrido a cuenta de Raja Koduri y Jim Keller, que son pesos pesados en el mundo de los semiconductores, durante el Día de Arquitectura 2018 que ha celebrado Intel con diversos medios.

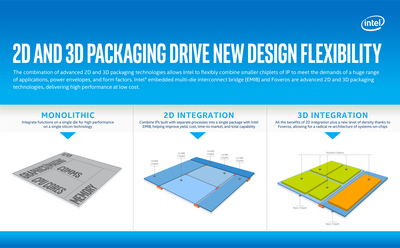

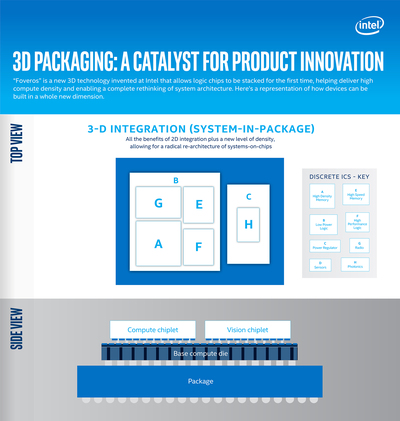

Pero yendo un paso más allá de lo que es simplemente unir varios chips en un mismo encapsulado, Foveros permitirá a estos bloques lógicos o chiplets ser apilados, ahorrando más espacio en el encapsulado y haciendo un conexionado mucho más directo entre ellos, lo cual tiene ventajas de consumo y latencia. Es una integración que denomina 3D, frente a la 2D que sería la usada por AMD para los próximos Ryzen y EPYC con núcleos de arquitectura Zen 2.

Intel se pone como objetivo para esta tecnología los sectores de procesadores de movilidad, como los Atom, que le permitiría combinar los chiplets de CPU, GPU, control, memoria y otros necesarios, con comunicación más específica como 5G, y todo en un encapsulado mucho más pequeño.

Como he dicho, el diseño de Foveros es por tanto una evolución de su tecnología EMIB (puente de interconexión multichip) de los Kaby Lake G, en el que el intermediador contendría las vías a través de silicio para el conexionado y sería un intermediador activo. Es una tecnología que Intel tiene ya muy perfilada, y de hecho ha mostrado en funcionamiento un par de chips desarrollados con Foveros.

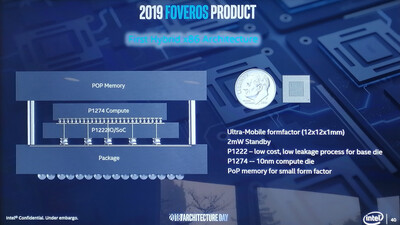

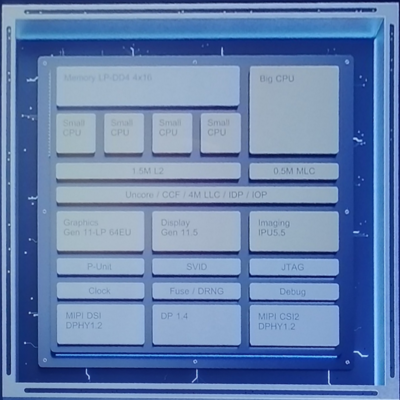

Se trata de procesadores Atom de movilidad —portátiles, tabletas, o incluso potencialmente teléfonos móviles—, con una arquitectura x86 híbrida, que permite tener un chíplet con un núcleo de mayor potencia y otro chíplet con núcleos de menor potencia. Sí, es el equivalente de Intel de la arquitectura big.LITTLE de ARM, usado en casi todos los procesadores de esta arquitectura de cierta potencia hoy en día. Ese procesador creado con chíplets y Foveros mostrado por Intel tiene un tamaño de 12 mm × 12 mm (144 mm2) con 1 mm de grosor, con un chip de E/S creado a 22 nm (22FFL) y otro a 10 nm con un núcleo Sunny Cove y cuatro núcleos Tremont, y un chip de memoria encima de ellos, y con un consumo inferior a los 7 W, y un consumo en espera a través del estado C6 de solo 2 mW.

Vía: AnandTech, Tom's Hardware, Intel.