Samsung habrá tenido un bajón de producción de semiconductores devolviendo el título de mayor productor a Intel, pero ciertamente está más avanzado en lo que a procesos litográficos se refiere. La compañía surcoreana ultima el proceso de fabricación de 5 nm, y el siguiente paso que ha dado ha sido la certificación de diversas herramientas de desarrollo de Cadence y Synopsis.

Estas herramientas incluyen compiladores, validadores, optimizadores de sistemas de alimentación y otras de luz ultravioleta extrema (UVE) necesarias para que las empresas puedan crear diseños de chips que hagan uso de este proceso de 5 nm de Samsung. Se espera que se finalicen de montar las líneas de producción a finales de 2019 y que la producción en masa de chips empiece en 2020.

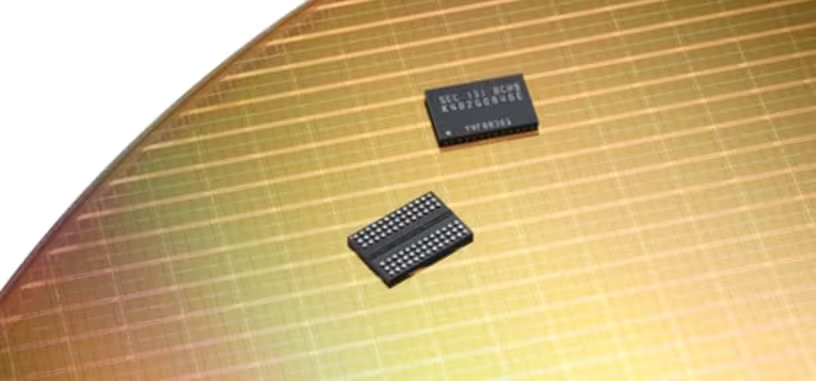

Cadence y Synopsis crean soluciones de desarrollo de chips que, inicialmente, hacen referencia a diseños de arquitectura ARM de núcleos de tipo Cortex-A53 y Cortex-A57 a esos 5 nm. A este nivel de integración Samsung va a utilizar transistores de tipo FinFET, pero cambiando ligeramente su diseño respecto a los 7 nm, y usa la luz UVE para las capas metálicas lo que reduce la complejidad de fabricación así como el tiempo de creación de cada oblea.

El proceso de 5 nm usará también un proceso de fabricación de patrones múltiples con luz ultravioleta normal para las capas más delicadas e importantes al ser una tecnología más madura. El desarrollo de chips es similar al de 7 nm, pero con la ventaja de que el nodo de 5 nm permite una reducción del área de hasta un 25 %, con un 20 % menos de consumo o un 10 % más de potencia respecto al proceso de 7 nm. Las herramientas de Cadence y Synopsis sirven para asegurar que los diseños de chips alcanzan un consumo óptimo, área y rendimiento dentro de lo establecido por Samsung para su proceso de 5 nm.

Vía: AnandTech.