Las necesidades de velocidad de interconexión entre dispositivos está haciendo que las empresas dedicadas a centros de datos estén impulsando el desarrollo rápido de nuevas versiones del estándar PCI Express (PCIe). En un momento en el que los consumidores todavía no tienen acceso a PCIe 4.0, aunque lo tendrán en unos días, las empresas están buscando la implementación de PCIe 5.0 y, en el caso del PCI-SIG (Grupo Especial de Interés de PCI), se ha anunciado el desarrollo de PCIe 6.0.

Esta nueva versión vuelve a duplicar la velocidad de PCIe 5.0, llevando la velocidad por canal a los 64 Gb/s (8 GB/s), cuadruplicando los 2 GB/s del estándar PCIe 4.0 que va a llegar con el chipset X570 y los procesadores Ryzen 3000 que se ponen a la venta el 7 de julio. Eso le dará a los dispositivos que tengan una conexión PCIe de dieciséis canales (PCIe ×16) un ancho de banda total de 128 GB/s.

En cierta parte, el renovado impulso de este estándar tiene que ver con la intención de Intel de usar la interfaz física de PCIe para su protocolo de nivel de enlace CXL, lo que ofrecerá una pila de protocolos más versátil a los dispositivos que se interconecten en los centros de datos. El protocolo ha recibido el apoyo de Dell, Facebook, Google, Lenovo, Cadence, SK Hynx, ARM, o Microsoft, entre otros, por lo que están muy interesados en aumentar al máximo el ancho de banda disponible para CXL, y eso se hace mejorando la interfaz física de PCIe con este nuevo estándar PCIe 6.0.

Pero todavía queda un par de años para que esté lista, ya que el PCI-SIG habla de que no estará lista la nueva especificación hasta 2021. El trabajo en realidad no se centra en lo habitual en estos casos, que es mejorar la integridad de la señal transmitida. Normalmente, al aumentar la frecuencia de funcionamiento de una conexión, es más difícil asegurar que cada bit se transmita en una ventana de tiempo más pequeña y también que se reciba y recomponga adecuadamente.

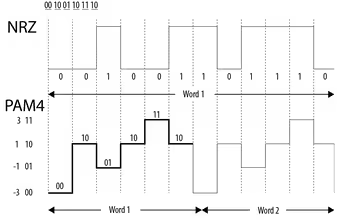

Pero en este caso, el PCI-SIG va a cambiar la señalización a PAM4 desde la NRZ (PAM2). Se mantiene por tanto la frecuencia de funcionamiento, pero en esta técnica de transmisión no hay solo dos voltajes posibles para indicar ceros y unos, sino varios para indicar cuatro estados (00, 01, 10, 11). Tiene ventajas también en que al funcionar de media a menores voltajes se introduce menos ruido en la transmisión, pero a cambio se precisa de mayor consumo en la circuitería de envío y recepción de la señal ya que tiene que ser más compleja para poder interpretar correctamente los cuatro estados posibles y no solo dos.

Eso también introduce una mayor posibilidad de interpretar incorrectamente un nivel de voltaje, lo que implica que estas conexiones deben tener menos longitud entre emisor y receptor. O, como es casi imposible en una placa base distanciar solo el procesador un par de centímetros con las ranuras PCIe, mejorar los filtros y sistemas de reconstrucción de la señal para asegurar que no hay errores por ruido en el canal. Por eso PCI-SIG va a incluir un código de corrección de errores para este estándar que es el de corrección de errores hacia adelante (FEC).

Vía: AnandTech.