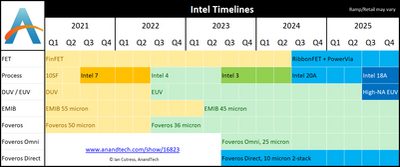

Pat Gelsinger, el flamante director ejecutivo de Intel y veterano ingeniero de la casa, apuesta el futuro de la compañía a su I+D y a un ambicioso itinerario de procesos litográficos. De momento está por ver si cumple los pasos más cercanos, pero los rumores dicen que la compañía tendría muy adelantado su proceso de 18 Å o (1.8 nm). Tanto como que iría seis meses por delante en su desarrollo.

Hay que tener en cuenta que los productos con chips fabricados con este proceso litográfico no estarían disponibles hasta 2025, y que en realidad depende de cuántas máquinas de luz ultravioleta extrema de alta apertura numérica pueda entregarle ASML para finales de 2024. Por mucho que vaya adelantado en su desarrollo, si luego no puede producir con él tendría el mismo efecto en el mercado: ninguno.

En IT Home se asegura que la producción en masa se producirá seis meses antes, pero eso no me lo creo en absoluto y es básicamente hablar por hablar. ASML no tendrá más que un puñado de máquinas de alta AN en 2024, del modelo TWINSCAN EXE:5200, y salvo que cambie la cosa no estarían instaladas y preparadas para producción en masa en 2025. Puede tenerlas instaladas en 2024, al menos algunas de ellas, pero lleva meses hacer los preparativos para la producción en masa, por mucho que tengan algún modelo anticipado en 2023 o 2024 para ir haciendo pruebas.

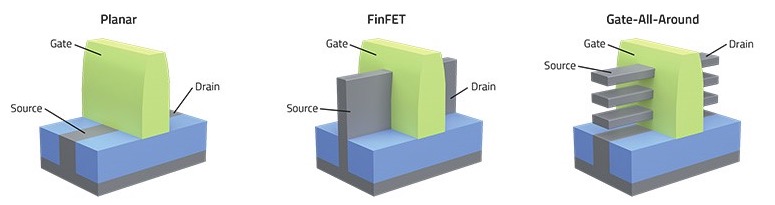

Este proceso de 18 Å usaría unos transistores construidos con nanoláminas que la compañía llama RibbonFET, y que no es otra cosa que unos GAAFET como los que va a usar TSMC en su proceso de 2 nm, o Samsung en su proceso de 3 nm y que la compañía llama MBCFET. Pero tengan el nombre que tengan son todos GAAFET (transistores de efecto de campo de puerta amplia), que son «transistores 3D». En estos el material que hace de puerta de los transistores rodea a varias nanoláminas o nanotubos apiladas, según el diseño específico, que hacen de fuente y drenador.

Más allá de los 1.8 nm, Intel va a tener que ser mucho más creativo. Actualmente se están desarrollando teorías a nivel académico para ver cómo se pueden crear nuevas formas que lleven a una reducción del tamaño de los transistores, o más bien de sus componentes. Pero son muy recientes, de 2019 hasta ahora, por lo que su implementación va a llevar mucho gasto de I+D y no se sabe si estarán listas para los plazos que se están marcando Samsung, Intel y TSMC.

Vía: WCCFTech.