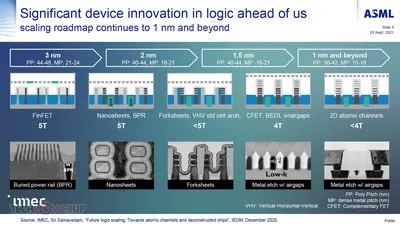

Los fabricantes de chips están teniendo que ingeniárselas para trascender a la actual estructura normalizada de los transistores, y sobre todo la muy utilizada estructura FinFET. Van a llegar al mercado los primeros chips en el que los transistores están apilados unos sobre otros, o más bien el canal en forma de nanoláminas o nanotubos (GAAFET), pero su estructura sigue siendo horizontal sobre el chip. IBM y Samsung han anunciado la implementación real de los VTFET (transistores de efecto de campo de transporte vertical) que trascienden a los GAAFET ya que las partes del transistor están creadas verticalmente.

Es una de las estructuras propuestas académicamente para conseguir llevar los procesos litográficos por debajo de los 1.5 nm. No tiene un nombre concreto, pero se usaría un CFET (FET complementario) y se modificaría los BEOL (contactos terminales de línea) para que los transistores se crearan verticalmente. Lo detallé en un artículo de ASML en el que la compañía de maquinaria litográfica se hacía eco de los avances que se estaban investigando en este sector.

IBM y Samsung hablan de que la reducción de consumo con este cambio de modelo de transistor sería del 85 % respecto a los actuales transistores de efecto de campo con aleta (FinFET). En parte se consigue al reducir la pérdida de energía en los contactos de los chips por la forma de fluir a través de los VTFET. En los tiempos actuales, una reducción tan sustancial del consumo tendría un impacto directo en todo tipo de sistemas, desde las comunicaciones hasta la criptominería.

Vía: TechPowerUp.