SK Hynix ha desarrollado junto a Intel y Renesas una nueva tecnología de acceso a módulos de memoria denominada multimplexación de filas combinadas (MCR, multiplexer combined ranks). Normalmente los módulos de memoria que tienen dos filas o hileras de chips accesibles de manera no simultánea debido a la conexión de 64 octetos con el procesador, o 72 con código de corrección de errores (ECC). MCR lo que permite es el acceso simultáneo a ambas filas, duplicando en la práctica la tasa de transferencia entre RAM y CPU.

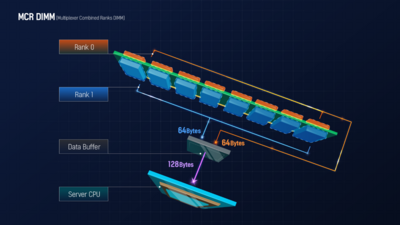

Una multiplexación es la fusión en un único flujo de datos de información de dos o más fuentes. Eso hace que la conexión con la CPU tenga que ser de 128 octetos para gestionar los 64 octetos de ambas hileras de manera simultánea, por lo que esto no estará disponible para los actuales procesadores de Intel sino para los próximos Xeon. En la práctica funciona como dos módulos de RAM en uno solo. En la siguiente imagen, la referencia a un «búfer de datos» es el multiplexador.

Se suele implementar dos filas en los módulos para permitir el doble de capacidad de lo normal. Pero eso tiene un efecto en el controlador de memoria, que lo estresa y por tanto no permite alcanzar velocidades tan altas que si se usara módulos de una fila de chips, salvo que sean placas base especialmente buenas. En la DDR5 la doble fila tradicional es una mala idea, al menos de momento, y esta MCR vendría a solucionar el problema.

El resultado es que prácticamente se duplica la velocidad, pasando de los habituales 4800 Gb/s hasta los 8000 Gb/s sin precisar de chips especialmente cribados para alcanzar esas velocidades. Aquí se habla de ancho de banda y no de frecuencia de funcionamiento de los chips, que por la información me imagino que serán de DDR5 a 4000 MHz. Pero como en la práctica está creando dos módulos de DDR5 en uno solo, la «velocidad sumada» viene a ser de «8000 MHz».