TSMC ha cogido distancia en el sector de la fabricación de chips con su proceso de fabricación a 7 nm, y no va a aflojar en su apuesta por el I+D. Teniendo en cuenta que solo Samsung y ella están manteniendo un ritmo de reducción litográfica de fabricación de chips, en 2020 van a llegar los primeros chips a una litografía de 5 nm de la mano de TSMC tras el anuncio de que ha finalizado el desarrollo de las herramientas necesarias para diseñar sistemas en chip (SoC) en esta litografía.

Esas herramientas incluyen manuales con reglas de diseño, kits de diseño de procesos y programas de simulación de circuitos integrados que están disponibles para sus clientes. La compañía previamente ha estado trabajando junto a varios clientes que no precisan de estas herramientas finalizadas y por eso ha indicado que también está haciendo pruebas de fabricación de varios diseños de chips personalizados, y por tanto se espera que llegue la producción en masa en 2020.

Este proceso de fabricación a 5 nm mezcla la creación de capas con un proceso ultravioleta profundo (UVP) como el usado en litografía superiores combinado con hasta catorce capas creadas con un proceso de litografía extrema (UVE). TSMC pone de ejemplo que con el proceso de 5 nm frente al de 7 nm se puede conseguir una densidad un 80 % mayor y una mejora de la velocidad del 15 % en los núcleos Cortex-A72, o conseguir una reducción del 20 % del consumo a misma frecuencia y complejidad de la planta del chip.

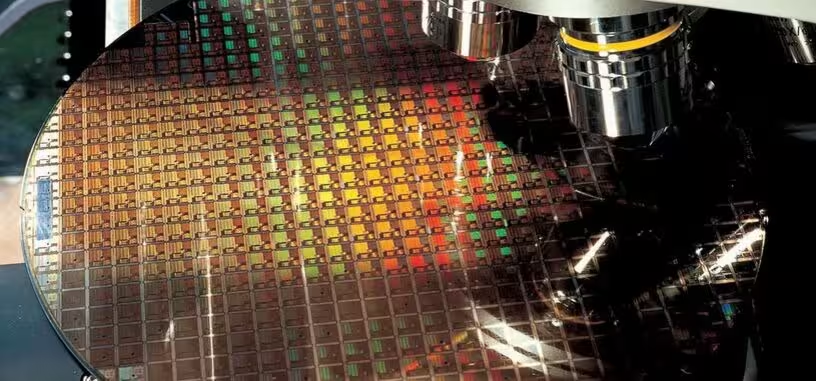

La mejora de uso de capas creadas con luz UVE han aumentado aunque todavía no se pueden usar para crear la totalidad de las obleas de las que se extraen los chips debido a diversos problemas de rendimiento de producción. Pero TSMC asegura que está aprendiendo rápidamente a cómo minimizar su impacto, y de ahí que a 5 nm aumenten el número de capas UVE y tenga que seguir usando las de UVP.

Vía: AnandTech.