Los fabricantes de memoria flash han estado explorando en los últimos años diversas formas de reducir la latencia de acceso para acercarla más al de la memoria NAND. Eso ha llevado a que Intel y Micron desarrollaran la memoria 3D XPoint, y que Samsung también tenga su memoria Z-NAND de baja latencia. Toshiba no se queda atrás, y ha anunciado el desarrollo de la memoria XL-Flash que reducirá notablemente la latencia de acceso a la memoria.

La memoria NAND normal dispone de celdas, las cuales se agrupan en Las celdas se agrupan en filas llamadas palabras, y estas a su vez en páginas. Una página es la cantidad mínima de información que se puede leer o escribir de una SSD en un momento dado. El tamaño de información que almacenan las páginas es de 4 KB u 8 KB, y las páginas están agrupadas en bloques que suelen tener un tamaño de 256 páginas, para un total de 2 MB. Por último, los bloques son agrupados en planos, generalmente de 1024 bloques, con varios planos por chip de memoria, generalmente dos o cuatro.

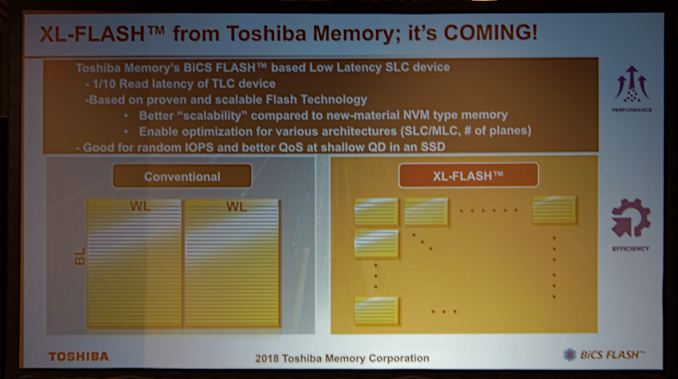

La idea de Toshiba es reducir la longitud de las palabras para crear chips con muchos más planos, lo que aparentemente reduciría un 90 % la latencia de acceso a la información. Se beneficiará notablemente la lectura/escritura aleatoria de información, o dicho de otra forma, el leer y mover archivos de pequeño tamaño, aumentando la cantidad de operaciones de entrada y salida por segundo (IOPS).

Usará XL-Flash a su memoria NAND, llamada BiCS —un acrónimo del inglés bit column stacked, o columnas de bits apiladas—, si bien estará inicialmente en uso con memoria de tipo SLC —un bit por celda— y MLC —dos bits por celda—. Debido a la orientación de baja latencia, que es de poca ayuda en el uso normal de un PC doméstico, esta memoria estará orientada a empresas y centros de datos, donde en estos últimos ciertas aplicaciones, como las de bases de datos, salen poderosamente favorecidas.

Vía: AnandTech.