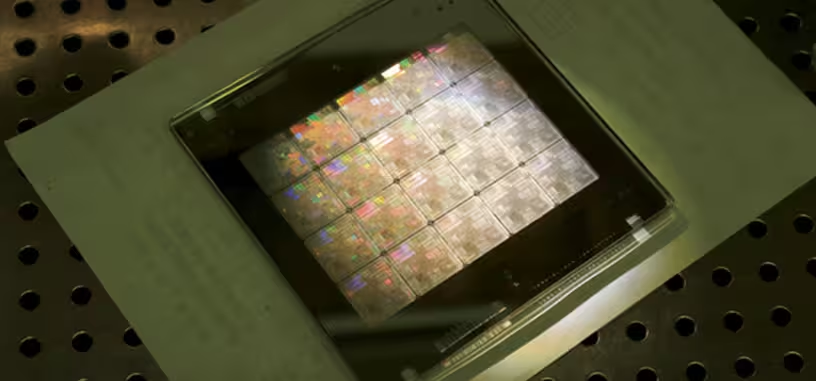

ARM actualizó en marzo la arquitectura big.LITTLE con una llamada DynamIQ. Mientras que la primera permite crear clústeres homogéneos de núcleos de mismo tipo, la segunda permite crear clústeres heterogéneos de núcleos de distintos tipos. Ahora TSMC, Xilinx, ARM y Cadence han anunciado que van a probar un chip fabricado en un nodo de 7 nm FinFET usando esta tecnología en el primer trimestre de 2018.

El centro de atención lo ponen en que es un chip para centros de datos, con el que también se va a probar una nueva interconexión coherente de caché para aceleradoras (CCIX), con el que comunicarán este chip multinúcleo con unas aceleradoras FPGA —un chip reprogramable más sencillo y eficiente que una CPU actual, terreno en el que Xilinx tiene mucha experiencia— externas de manera que se mantenga la coherencia de la información accedida por el conjunto —que siempre tengan acceso a la información más actual de la procesada por todo el sistema en la memoria principal—.

La idea subyacente es que se puedan comunicar con esta interconexión chips de distinto tipo, haciendo que cada chip procese la información para la que esté más preparado. Es un punto importantísimo para los centros de datos, que suelen manejar cantidades ingentes de información de todo tipo, y normalmente terminan ejecutando información en un procesador cuando podrían hacerlo en una FPGA si pudieran asegurar la coherencia de la información.

Prometen un mayor ancho de banda y menores latencias de acceso con su nuevo CCIX. El chip usa núcleos basados en la arquitectura ARMv8.2, la interconexión CMN-600, con memoria DDR4 y acceso a pistas PCIe 3.0/4.0 a través de controladores proporcionados por Cadence. Si todo sale bien, tras las pruebas del T1 de 2018, el chip se pondrá a la venta en la segunda mitad del año.