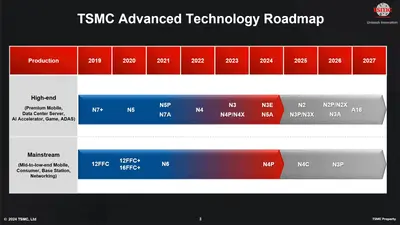

TSMC ha sido bastante clara a la hora de decir que no tiene prisa a la hora de utilizar la maquinaria de alta apertura numérica en sus próximos procesos litográficos. A razón de más de 300 millones de dólares por escáner de alta AN, el precio de la oblea se dispararía incluso usándolo solo en un puñado de capas. Intel va a ser la primera que las use porque las necesita: sus litografías ahora mismo no son competitivos frente a las de TSMC. Samsung aún más, porque sus litografías dan pena —lo siento, es la dura realidad—. Por eso que TSMC diga que para su recién anunciado proceso de 1.6 nm no va a usarlas no es ninguna sorpresa.

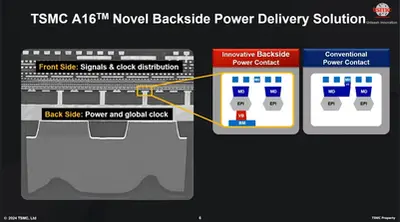

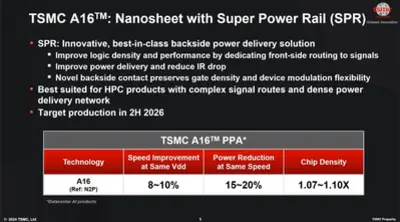

Este proceso litográfico, llamado A16 por adoptar un nuevo formato por los ángstroms (Å) en que se van a medir, será un importante salto tecnológico porque será el primero en el que la compañía use la entrega trasera de energía (backside power delivery), lo cual supone rehacer cómo se alimentan los transistores para ganar estabilidad de señal y reducir las pérdidas de energía en su transporte hasta estos. Esto va a ser implementado en breve tanto por Intel como por Samsung, con la esperanza de alcanzar a TSMC en las características de sus transistores.

TSMC llama a esta tecnología super power rail (SPR), pero es la entrega trasera de energía de toda la vida. La diferencia radica en cómo se hace exactamente esa entrega. En el modelo general hay un canal de energía enterrado en la trasera del chip al que posteriormente se conectan los transistores mediante vías a través de silicio. Intel le da un pequeño giro en PowerVia al hacer una conexión más directa, lo que mejora la entrega de energía pero hace más complejo el enrutamiento de las pistas.

En el caso de SPR, conecta la red de entrega trasera de energía tanto a la fuente como al drenador de los transistores ya que lo considera lo más eficiente a expensas de aún más complejidad que con PowerVia. TSMC evitó dar fecha de llegada a SPR, para luego decir que llegaría en el nodo N2P, y ahora lo ha retrasado al A16 por la gran complejidad que tiene su implementación. Y que tampoco lo necesita realmente para mejorar el nodo N2P. Al aplazarlo al A16, eso significa que también abarata el N2P, cosa que ni Samsung ni Intel van a poder hacer —salvo que vendan a pérdidas, que es una táctica habitual de Samsung Foundry y ya se verá si también de Intel Foundry—.

Ha compartido algunos objetivos de mejora de este proceso litográfico respecto al N2P. Con este cambio, y algunos otros, mejoraría la frecuencia de los chips un 8-10 % a mismo voltaje, reduciría el consumo un 15-20 % a misma frecuencia, y la densidad de los chips aumentaría un 7-10 %, que no es gran cosa. El problema actual sigue siendo reducir lo que ocupan las celdas de memoria, principalmente la SRAM y todo lo derivado de ello, como las cachés. Y teniendo en cuenta que las cachés van siendo cada vez más porcentaje de los chips porque no se puede reducir lo que ocupan, al final las mejoras en densidad de chip son más discretas, aunque sean sustanciales para la parte de los transistores.

El A16 debería llegar al mercado más bien en 2027, pero antes tienen que llegar el N2 en 2025.

Vía: Tom's Hardware.