Con el cambio a los transistores de efecto de campo de puerta envolvente (GAAFET) se está dando un gran paso adelante en la fabricación de microchips. Son un paso necesario para mantener un cierto ritmo en los próximos años de aumento de potencia, reducción de consumo y aumento de la densidad de transistores en los microchips. Pero se precisa de hacer cambios adicionales en algún momento, y uno de esos cambios es la entrega de energía a los transistores desde la trasera del chip.

Intel va a ser la primera empresa en añadir esto a sus chips, y será en 2024 en el proceso 20A (2 nm). Los primeros chips serán los procesadores Arrow Lake, que llegarán a mediados del año. Samsung lo está preparando para su proceso de 2 nm, y TSMC lo añadirá a la segunda generación de su litografía de 2 nm. Ahora la compañía ha dado más detalles sobre su implementación de esta tecnología, aunque antes de hablar de ello voy a pararme un momento para hablar en un par de párrafos de en qué consiste.

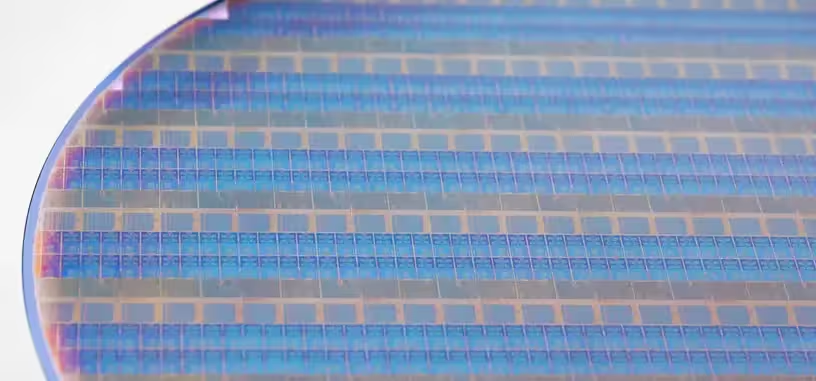

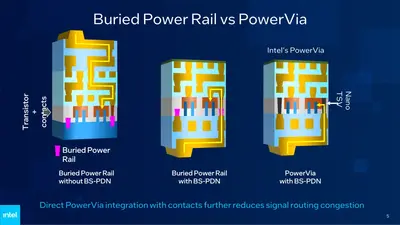

Esta tecnología de entrega de energía en la trasera del chip (backside power delivery) permite alimentar los transistores directamente en las capas inferiores donde se crean —luego al chip se le da la vuelta para encapsularlo y quedan arriba, pero estoy hablando de cómo se crean las obleas—, en lugar de tener que atravesar la energía por capas y capas de componentes y pistas.

Se consigue aumentar la integridad de la señal entregada en la trasera al reducir el ruido en el frontal del chip —las capas superiores de la oblea, o la inferior del chip encapsulado—, con menores pérdidas y una mayor densidad del chip al eliminar capas o estructuras de entrega de energía más largas. Pero las desventajas son que aumenta la complejidad de fabricación de la obela, tanto por maquinaria necesaria como pasos extras en la producción de las obleas, además de que puede haber mayor cantidad de defectos, y que no se puede usar con todos los tipos de chips.

Los GAAFET en terminología de Intel se llaman RibbonFET, porque en lugar de nanocilindros apilados para hacer de puerta y drenador —dos de los terminales de un FET—, son nanoláminas apiladas las cuales luego son envueltas por una puerta común —el otro terminal de un FET—. Intel ha hecho las pruebas iniciales de PowerVia, la tecnología de los GAAFET con entrega de energía trasera, con su proceso de 4 nm.

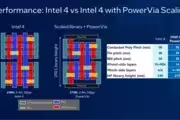

De entrada, con el uso de PowerVia añade complejidad a la fabricación, con pasos extras. Si las capas metálicas del frontal, las encargadas de alimentar los transistores y otras estructuras, son habitualmente de quince más una capa de redistribución de energía, usando PowerVia las capas del frontal se reducen a catorce, y se pasa la capa de redistribución a la trasera, añadiéndose cuatro capas extras de alimentación.

La parte inferior de la oblea luego es limada para exponer los contactos de la red para la redistribución de energía. La entrega de energía al chip se sigue haciendo desde el frontal —al voltearlo, la parte inferior del chip en contacto con el sustrato—, pero a través de una vía a través de silicio que atraviesa directamente todas las capas hasta las de la trasera. Esas vías son conectadas después con la red de distribución de energía que alimenta a los transistores mediante microcontactos que se crean durante la finalización de la oblea o el chip.

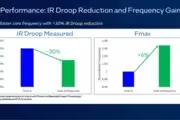

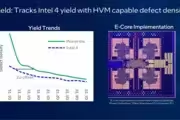

Este proceso Intel 4 más PowerVia ha sido utilizado para crear el chip Blue Sky Creek, un modelo con cuatro núcleos de eficiencia funcionando a 3 GHz y 1.1 V. Lo que ha visto Intel, y como he comentado antes como algo normal en la entrega de energía en la trasera de los chips, es que hay una mayor cantidad de defectos por oblea. Intel ha trabajo duro en reducirlos desde que empezó las pruebas de producción de PowerVia en el T1 2021 hasta acercarlos notablemente a la densidad de defectos que tiene el proceso de 4 nm.

Sobre el otro problema, el del calor por la reducción de silicio en la trasera del chip para exponer los contactos de la red de distribución de energía, ha indicado que no han visto que haya aumentos significativos.

Donde Intel ha tenido más problemas es en la detección de errores del proceso de fabricación y del diseño de los chips, desarrollando nuevas herramientas para la validación del diseño de chips, que será realmente importante para Intel Foundry Services, su servicio de fundición para terceros. Porque no hay que olvidar que ahora Intel necesita pasos adicionales en el desarrollo de procesos litográficos para asegurarse de que son fáciles de entender y que es fácil de desarrollar chips para ellos.

Vía: Tom's Hardware.