IBM realiza una fuerte inversión en I+D+i y eso se suele hacer notar en sus diseños de procesadores. Son modelos para empresas, principalmente centros de datos hoy en día, pero suelen tener siempre alguna particularidad interesante respecto al resto de procesadores del sector. En el caso del nuevo procesador Telum, lo curioso es que prescinde totalmente de la caché de nivel 3 habitual en otros procesadores para ganar rendimiento, aunque pueda parecer una contradicción.

En la caché se almacena información que está siendo usada por un núcleo o que va a ser previsiblemente usada en un corto espacio de tiempo, al menos al hablar de la caché de nivel cero y uno. La caché de nivel dos suele ser donde va la información expulsada de la de N1 para hacer hueco a nueva información traída de memoria, y es bastante más rápida que la de nivel tres. El uso de esta última en las arquitecturas de Intel y AMD es distinta, pero es común a todos los núcleos y suele mejorar notablemente el rendimiento.

Por cómo funcionan las cachés de un procesador, cuanto más grande es más latencia introduce porque hay que consultar un registro mayor de dónde está la información que va a usar el núcleo, y a su vez la información puede estar más lejos del núcleo en sí lo que introduce latencia adicional. También, cuanto mayor es la caché existe un aumento exponencial de lo que ocupa en la planta de chip, que es lo que evita que haya cachés de nivel cero enormes, o que toda la caché sea de N0. Es en ambas partes donde IBM innova prescindiendo de la de N3.

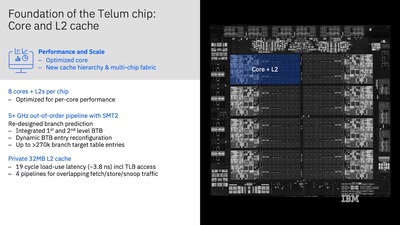

Lo que hace la compañía en el procesador Telum es incluir ocho núcleos a más de 5 GHz y cada uno con 32 MB de caché privada de N2. El chip está fabricado con un proceso de 7 nm. Un Ryzen tiene 512 KB de caché de N2 por núcleo, por lo que es muchísima más. En el proceso, aumenta la latencia solo de 12 ciclos de acceso a 19 ciclos lo que se traduce en unos 3.8 ns. No es un gran aumento gracias a un rediseño interno del chip. Esto significa que Telum tiene 256 MB de caché de nivel 2, cuando un Ryzen 5800X tiene 4 MB y 32 MB de caché de N3.

Pero IBM va un paso más allá, y esta caché de N2 no es del todo privada sino que las ocho cachés de 32 MB están conectadas mediante una topología en anillo bidireccional con una interconexión de alta velocidad de 320 GB/s. Cuando se expulsa algún dato de una caché de un núcleo se puede reubicar en la caché de algún otro núcleo como si fuera una caché de N3, dejándola marcada con la etiqueta de que es de N3 para que se tenga en cuenta a futuro. Por tanto, la caché de N2 del Telum es una caché de uso híbrido, y no mucho más lenta que en otros procesadores convencionales, siendo una «caché de N3 virtual» de 256 MB.

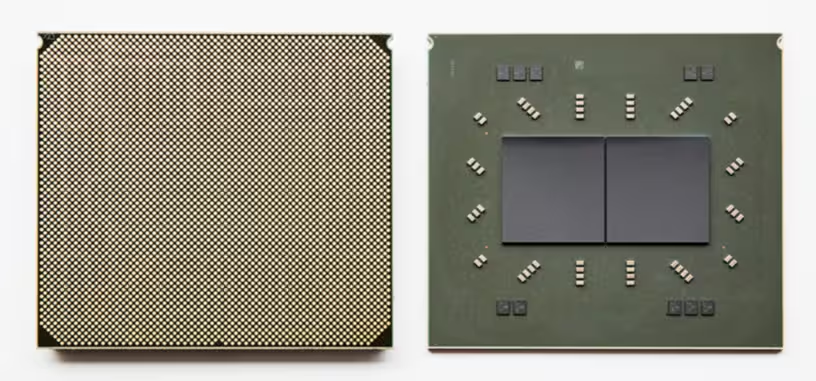

El chip Telum se encapsulará de dos en dos con una interconexión de alto rendimiento por lo que el procesador finalmente tendrá dieciséis núcleos y 512 MB de caché de N2. Estos procesadores tienen sobre todo su uso en unidades centrales que son altamente fiables por los diversos sistemas de redundancia y control de errores que tienen —solo se caen algunos milisegundos al año—. Incluye una aceleradora de inteligencia artificial para ayudar en las tareas de inferencias con una potencia de 6 TFLOPS.

Vía: Ars Technica.