Últimamente de lo que hablamos en los comentarios de la web termina convirtiéndose en noticia a los pocos días. Ayer mismo estábamos hablando sobre los programas que permiten optimizar el diseño de chips y hoy hay una noticia sobre ello de la mano de Cadence. Ciertamente no es la habitual noticia del sector tecnológico y de ahí la extraña coincidencia. La compañía ha anunciado Cerebrus, una herramienta que permitirá a las compañías hacer el diseño de los chips de una manera mucho más rápida y eficiente, pero también en tiempos récord.

Cerebrus utiliza aprendizaje automático para realizar un proceso exhaustivo de colocación y testeo de los elementos de un chip con el oportuno ruteo entre componentes. Aquí no es tanta la novedad de que ponga y optimice la disposición de componentes como la parte de inteligencia artificial. Desde hace años, o décadas, las herramientas de diseño de placas o chips permiten automatizar el posicionamiento y creando de rutas y vías entre varias capas de placas base y chips.

El problema de hacerlo con esas herramientas es que precisa bastante supervisión para que el ingeniero —más bien ingenieros en los proyectos grandes— se asegure de que todo está debidamente colocado y que va a funcionar perfectamente. Cerebrus simplifica ese procedimiento manual de validación que requiere de múltiples ingenieros en proyectos importantes y lo reduce a un solo ingeniero para que valide el diseño final.

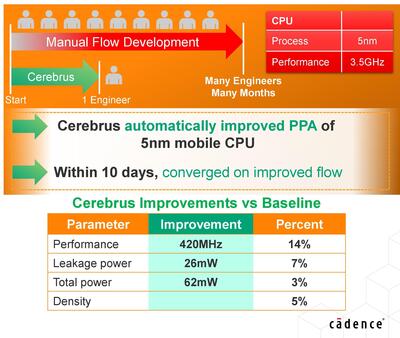

Esto supone un enorme ahorro de tiempo y dinero para los diseñadores de chips, y además lleva a ganancias en diversos aspectos del diseño, que era también lo que mencionaba en los comentarios. Un chip suele sufrir modificaciones en su proceso de diseño e incluso en el de pruebas de producción para ganar rendimiento, consumo y optimización de área. Es lo que se define con la sigla PPA (power, performance, area), en la que en un diseño de ejemplo a 5 nm Cerebrus consigue un 14 % más de frecuencias, un 7 % menos de corriente de fuga, un 3 % más de consumo total para apoyar la mejora de rendimiento, y la densidad de transistores mejora un 5 %.

Esos resultados se consiguen en diez días por un ingeniero y Cerebrus frente a meses de planificación y optimización por una decena de ingenieros y las herramientas actuales de diseño de chips. Se trata de un caso de uso real de un cliente de la compañía, probablemente usando la fundición de Samsung —si antes digo que Samsung seguía verde en este terreno, antes aparece Cadence con el carrito de los helados para pasarme por encima—.

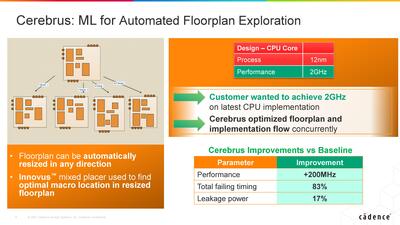

También se ha mencionado otro caso de uso, en este caso de optimización de un diseño de núcleo de CPU a 12 nm en el que el cliente quería que funcionar a 2 GHz con el menor consumo y área posible. Cerebrus fue capaz de alcanzar esa frecuencia reduciendo un 83 % las rutas en las que no se cumplen los tiempos de comunicación y reduciendo también la corriente de fuga en un 17 %.

Estas herramientas precisan de bastante información de las estructuras lógicas a usar, procesos litográficos, longitud prevista de las conexiones entre componentes, distribución de energía y muchos otros, por lo que automatizar la completa automatización no es posible. Para ayudar a los ingenieros, Cerebrus incluye un registro con cada iteración que hace y explica los motivos de porqué mueve, pone o quita cosas para que el ingeniero que revise el diseño final entienda cómo se ha llegado a él. Eso sí es bastante único de esta herramientas.

Hay otras de otras compañías que también usan inteligencia artificial para mejorar los diseños, pero el diseño de chips es algo tan complejo que solo se están dando los primeros pasos en ello. Synopsis es otra grande en este terreno, y como Cadence está dando casi sus primeros pasos. La diferencia es que Cerebrus está ya disponible para una base de clientes mayor, y la herramienta DSO.ai de Synopsis sigue en desarrollo —léase «en pruebas con un selecto número de clientes»—.

Vía: AnandTech.