Nvidia ha presentado las primeras GeForce RTX 30 pero ha hablado bastante poco de la arquitectura en sí, dando solo generalidades. Hasta que se publique el libro blanco de Ampère para las GeForce, que es una arquitectura distinta de la incluida en el chip A100 para cómputo, habrá todavía diversas incógnitas. Y aún cuando publique el libro blanco quedarán bastantes preguntas sin respuesta. Sea como sea, la publicación de una presentación de las GeForce RTX 30 arroja un poco más de luz sobre Ampère.

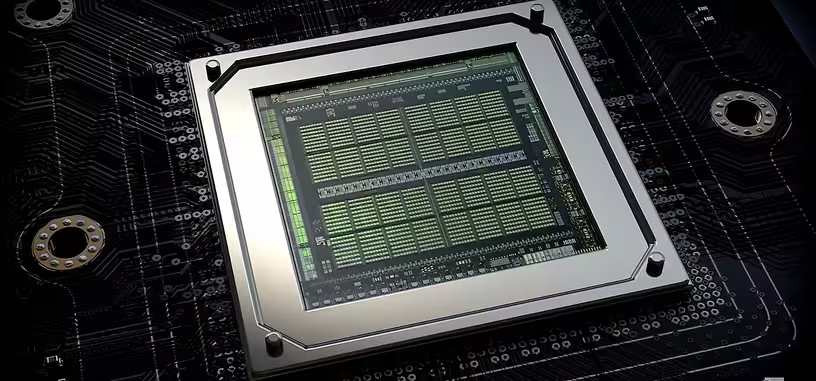

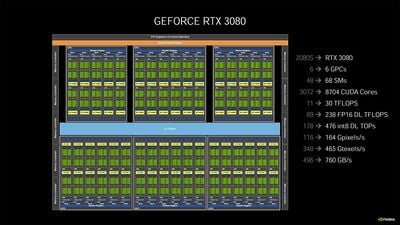

Empezando por los chips en sí, el GA102 de las RTX 3080 y 3090 tiene un tamaño de 628 mm2, que es un buen recorte frente a los 754 mm2 del TU102 de la RTX 2080 Ti. Recordad que cuanto más pequeño es un chip más salen de cada oblea y más beneficios obtiene Nvidia, por lo que al combinarlo con un proceso de 8 nm de Samsung no tiene pinta que el GA102 sea un chip especialmente caro, y probablemente bastante más barato inicialmente que el TU102. En ese tamaño entran 28 000 millones de transistores en el GA102 en vez de los 18 600 millones del TU102. El chip GA104 de la RTX 3070 tiene un tamaño de 392 mm2 y cuenta con 17 400 millones de transistores.

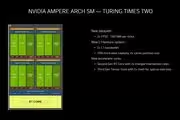

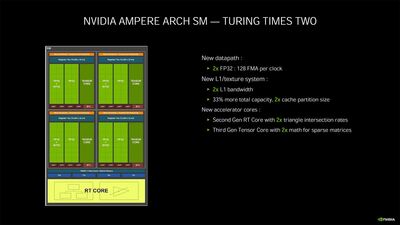

El multiprocesador de flujo de datos (SM) de la nueva arquitectura Ampère para las GeForce incluye bastantes cambios. De entrada, incluye cuatro grupos de «núcleos CUDA» como hasta ahora, pero las dieciséis unidades aritmético-lógicas INT32 de cada uno se convierten en otras dieciséis FP32 completas, por lo que ahora cada SM incluye cuatro grupos de 32 núcleos CUDA. Lo gracioso de la implementación es que uno de los grupos puede ejecutar una urdimbre de dieciséis instrucciones INT32 a la vez que otra urdimbre de instrucciones FP32.

Eso significa que duplica la potencia de cómputo en FP32 cuando sea necesario, pero se mantiene la posibilidad de ejecutar instrucciones INT32 de manera algo más eficiente cuando sea necesario. No es cien por cien eficiente porque es un circuito FP32 para ejecutar cálculos INT32 mucho más sencillos, pero algo hace. En la arquitectura Turing, en un momento dado solo se podía ejecutar una urdimbre de dieciséis hilos INT32 y una urdimbre FP32. En la práctica es duplicar los núcleos CUDA, como está indicando Nvidia, por lo que en realidad no hay pegas hacia la afirmación de Nvidia: se duplican los núcleos CUDA de la arquitectura Turing.

Para poder alimentar a este sistema, que es un distanciamiento de lo que se venía haciendo hasta ahora en los SM, la compañía ha duplicado el ancho de banda de la caché de nivel 1, ha añadido un 33 % más de capacidad y ha duplicado el tamaño de la partición de caché. Son los cambios que, efectivamente, necesitaría hacer para que el grupo de FP32 y el de INT32 funcionaran a la vez, porque sería como ser dos grupos totalmente independientes de núcleos CUDA. La decisión de integrar ese segundo grupo de dieciséis FP32 es que comparten un único núcleo tensorial, y el SM incluye un núcleo de trazado de rayos. Hacerlo de otra forma habría sido poco rentable, porque esto también significa que se pueden ejecutar urdimbres de 32 instrucciones en paralelo, lo cual es mucho más eficiente que ejecutar una de 16 como hasta ahora.

De entrada el cambio en el SM es mayúsculo, pero no se han quedado ahí las cosas. La compañía habla de que se ha duplicado la potencia de trazado de rayos del nuevo núcleo, y también se duplica la potencia del núcleo tensorial en esta nueva generación. Además, la compañía ha modificado la tubería de ejecución del trazado de rayos con un nuevo paso que es la interpolación de la posición de un triángulo en el tiempo y no solo en el espacio para averiguar si un rayo incida en sus píxeles y modificar su color de la manera apropiada.

Eso significa que con información realimentada puede crear efectos de desenfoque de movimiento para mejorar ciertos efectos de la luz en su incidencia con superficies. Esto se realiza durante el recorrido de la jerarquía de delimitadores de volúmenes (BVH, bounding volume hierarchy), siendo esa jerarquía simplemente una división de zonas de una imagen con los objetos geométricos que están en ella con diversas subdivisiones si son zonas complejas y en los nodos inferiores se ubican los propios objetos geométricos en sí. Con información temporal de cada nodo del BVH se puede determinar el desenfoque resultante de manera más precisa para crear escenas más realistas.

Nvidia habla de que en el paso de Turing a Ampère se ha mejorado el rendimiento por vatio un 90 %, aunque lo hace con una comparativa un poco extraña que no me termina de quedar claro pero que es claramente engañosa. El paso del proceso de 12 nm de TSMC al de 8 nm de Samsung ha aplicado en torno a un 40 % de reducción de consumo, y ha modificado poco las frecuencias (unos 150 MHz más de turbo RTX 2080 Ti a RTX 3080), por lo que casi toda la mejora de rendimiento de esta generación procede de duplicar los núcleos CUDA. Y encaja (en mi cabeza). Si a los 250 W de la RTX 2080 Ti se calcula el 60 % (150 W) y se multiplica por el doble de CUDA el resultado son 300 W. Con los cambios de consumo de los núcleos tensoriales y trazado de rayos, la RTX 3080 tiene 320 W de consumo. Por tanto, es ridículo hablar que se ha mejorado un 90 % el rendimiento por vatio, sino que se ha quedado en el de Turing: no hay excesiva mejora de las instrucciones ejecutadas por ciclo (IPC). Eso probablemente se quede para la siguiente generación GeForce RTX 40.