La memoria de alto ancho de banda —HBM, por sus siglas en inglés— no ha tenido tanto uso como AMD pensó que tendría cuando empezó a colaborar con Samsung y SK Hynix en su desarrollo. Solo un puñado de dispositivos la usan, como las tarjetas gráficas con unidad gráfica de arquitectura Vega o los procesadores Kaby Lake G de Intel. En parte porque la GDDR ha seguido evolucionando y la GDDR6 tiene ventajas de coste respecto a ella. Aun así, la Asociación JEDEC de Tecnología de Estado Sólido ha realizado una revisión del estándar para mejorarlo de cara a los fabricantes.

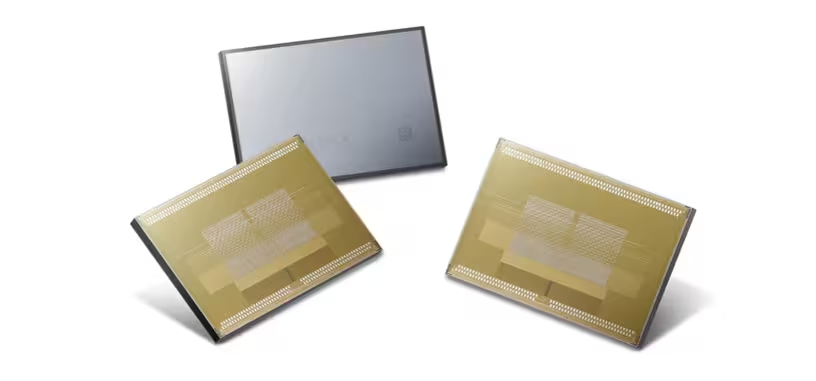

Los chips de memoria siempre suelen crearse mediante apilación de capas de memoria, y en esta ocasión la JEDEC pasa a especificar cómo se pueden establecer ahora hasta doce capas apiladas de HBM, lo que permite en la práctica crear chips de mayor capacidad, ahorrando espacio. La conexión se hace mediante conexionado a través de silicio (TSV) entre 2, 4, 8 y 12 capas, para un total de 1 GB a 24 GB por chip, en función de la capacidad de cada capa.

También se mejora la velocidad de comunicación, que pasa a ser de 2.4 Gb/s por pin, que en chips de 1024 bits implica que se alcanzan los 307 GB/s por chip incluido en un sistema. En las unidades gráficas Vega con dos chips, el ancho de banda máximo sería de 614 GB/s, frente a los 484 GB/s actuales.

Vía: The Tech Report.