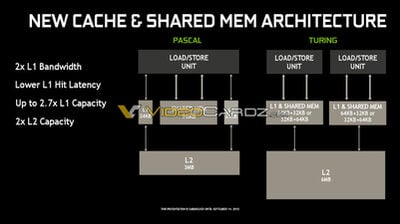

La mayor parte de la arquitectura Turing usada en las nuevas GeForce RTX es desconocida ahora mismo, si bien el 14 de septiembre se sabrá mucho más en cuanto lleguen los primeros análisis. Junto a ellos, los diagramas de bloques y otra información sobre su funcionamiento interno, y ahora ha sido publicada una transparencia en la que se detallan cambios en la jerarquía de la memoria caché de los multiprocesadores de flujo de datos (SM) de Turing.

Cada SM, que es una envoltura que incluye los núcleos CUDA, los tensoriales y otras unidades necesarias como las de carga/guardado, también incluye una memoria caché de nivel 0 (L0) por estructura agrupada de varios CUDA. A la derecha tenéis la estructura del SM de Volta, y el de Turing será similar. En este caso, cada SM tiene una memoria caché de nivel 1 (L1) de 128 KB, réplica de la de Volta, aunque es configurable.

La caché L1 incluye la información que va a ser utilizada inmediatamente por los núcleos CUDA asociados, y es no coherente, lo que significa que la información no está sincronizada entre los distintos SM. Hasta ahora había una memoria compartida, que sí es coherente, y que además es mucho más rápida de usar que la L1. En Turing se unifica la memoria L1 y la compartida, aunque eso significa que queda a manos de los programadores decidir cómo utilizarla.

La ventaja más directa de esto es que, puesto que esa memoria unificada tiene mayor ancho de banda, el movimiento de información entre la L1 y los registros de los CUDA es más rápida, o dicho de otra forma, tiene menor latencia de acceso. Son optimizaciones que pueden parece nimias, pero que son muy importantes porque reducen la cantidad de ciclos de reloj que se requiere para la ejecución de las operaciones atómicas en las ALU de los SM (los núcleos CUDA). Nvidia indica en la transparencia que el ancho de banda de la caché L1 se duplica, y por tanto tiene una latencia menor a la hora de obtener aciertos de caché —que la información que buscan las unidades de carga/guardado esté en este caché L1—.

Si no está la información en la caché L1, se procede a mirar en la caché de nivel 2 (L2). En esta ocasión, Turing duplica la capacidad de la caché L2 de los 3 MB de Pascal a los 6 MB, lo que significa que va a haber una mayor cantidad de aciertos de caché L2 si la caché L1 intenta buscar información necesaria para la ejecución de las urdimbres en la SM —conjuntos de treintaidós hilos que se ejecutan simultáneamente—. La búsqueda y ejecución simultánea de información lo que permite es ahorrar ancho de banda de las distintas memorias, y es lo óptimo en las unidades de procesamiento gráfico (GPU), si bien en las unidades centrales de procesamiento (CPU) no se hace así.

Nvidia ha optado por no aumentar la cantidad de memoria de las tarjetas gráficas GeForce RTX, y ya apuntaba a que debía de haber realizado cambios a nivel de hardware para reducir el uso de memoria VRAM. Aunque no hay por el momento datos concretos sobre la compresión de memoria usada u otros métodos que reducen su uso, es bastante prometedor estos cambios a nivel de caché. Si aumentas la caché L2, evitas tener que acceder a la memoria principal de la tarjeta gráfica más veces, lo que significa que se reduce de hecho el ancho de banda consumido por los SM.

Aunque con la memoria GDDR6 de 14 Gb/s incluida en las GeForce RTX han aumentado sustancialmente este ancho de banda, estos cambios de caché reducen de manera significativa su uso, lo cual es fundamental para un buen funcionamiento de las nuevas unidades incluidas, núcleos tensoriales y núcleos de trazado de rayos, que también hacen uso de ese ancho de banda para funcionar correctamente. Pero toca esperar un poco más para saber los cambios específicos que Nvidia ha hecho al uso y disfrute de la VRAM de las tarjetas gráficas GeForce RTX.