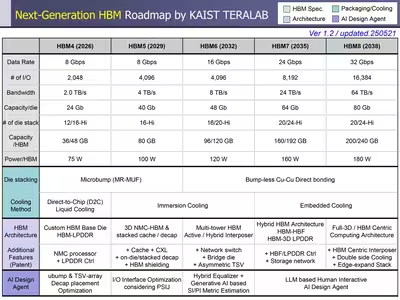

La memoria de alto ancho de banda (HBM) está desarrollándose a pasos agigantados por las necesidades actuales de las aceleradoras para inteligencia artificial. Cuanta más memoria, con más parámetros de entrada pueden ser entrenadas las IA, y eso redunda en su precisión y capacidades. Así que el nuevo plan para la evolución de la HBM publicado por el Instituto Avanzado de Ciencia y Tecnología de Corea (KAIST), una universidad pública centrada en la investigación, sitúa el lanzamiento de la HBM7 para 2035, y la HBM8 para 2038.

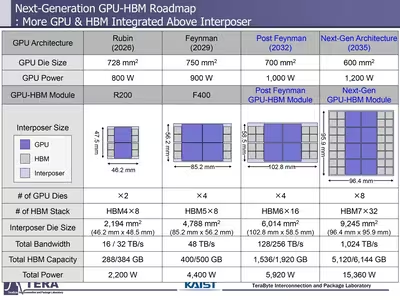

La tendencia es a que los métodos de encapsulación avanzados vayan permitiendo introducir más y más chíplets de GPU por encapsulado, y a que esas GPU usen cada vez más HBM, para conformar unas aceleradoras que serán unos auténticos monstruos de la computación. Pero a un alto precio, como es el consumo que van a tener, lo cual significa que el consumo de los centros de datos va a explotar en la próxima década.

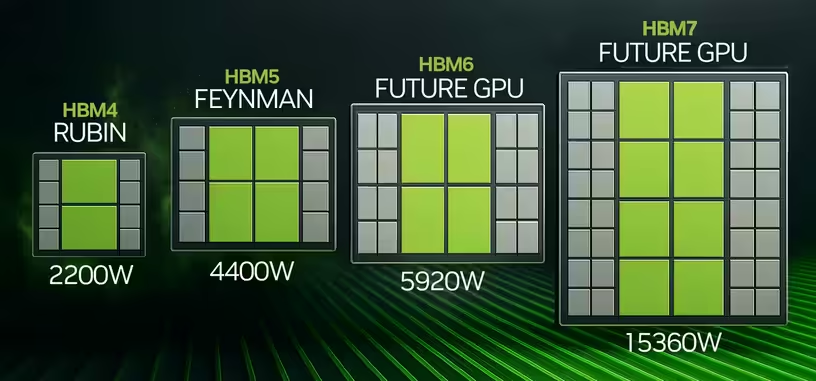

Los chips de HBM7 consumirían 160 W cada uno, y se combinarían con ocho GPU de 1200 W estimados para un consumo de 15 360 W por aceleradora, con una cantidad de HBM en torno a los 6 TB. NVIDIA está preparando para 2026 una aceleradora de 2200 W, compuesta por dos GPU de 800 W y ocho chips de HBM4 de 75 W cada uno. Después llegaría en 2029 la HBM5 de 100 W por chip, y en 2032 la HBM6 de 120 W. TSMC ya tiene en cuenta este tipo de encapsulados, porque está desarrollando métodos para crear encapsulados realmente grandes, como los indicados por el KAIST, porque este prevé que las aceleradoras de 2035 midan prácticamente 10 cm × 10 cm.

Vía: Videocardz.