Intel ahora es menos proclive al secretismo que hace diez años debido al cambio de dirección que ha tomado la compañía con Pat Gelsinger al mando. Por eso se conoce el itinerario de la compañía para los próximos años, con nombres de generaciones de procesadores, algunas de sus características, y lo que va a hacer en cuanto a litografías, aunque no da todos los detalles. Para los Meteor Lake, que comercialmente son los primeros procesadores Core Ultra, es ahora cuando Intel los ha presentado oficialmente dando esos interesantes detalles.

Los primeros portátiles con estos procesadores llegarán a las tiendas el 14 de diciembre, por lo que Intel va a cumplir casi con el final de año su promesa de ponerlos en el mercado. Probablemente en un volumen bajo, salvo sorpresas. Los detalles de los modelos específicos se darán más cerca de su lanzamiento. Se llaman Core y Core Ultra seguidos de un número —los habituales 3, 5 y 7 por ahora—, por lo que deja atrás la «Core i».

Estos Meteor Lake tienen la ya conocida estructura de chíplets a las que Intel llama teselas (tile) como si conformaran un mosaico. Me quedo con el nombre de chíplet porque es el estándar de la industria. Es como si Intel llamara «baldosa» a los chips. No hay que seguirle el juego a Intel.

Los chíplets incluidos en estos procesadores son cuatro: gráficos, sistema en chip, E/S y computación. Además de estos, hay un chip que hace de interconexión con la tecnología de módulos multichip Foveros 3D, el cual está fabricado a 16 nm (Intel 16), que es como llama ahora al antiguo proceso 22FFL (22 nm fin-FET low-power).

Computación

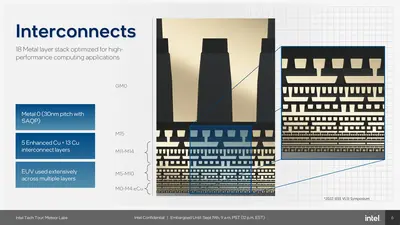

El chíplet de computación está fabricado por Intel a 4 nm (Intel 4) con maquinaria de luz ultravioleta extrema (UVE) en varias capas, mientras que el resto están fabricados por TSMC: el de la GPU a 5 nm y los otros dos a 6 nm. Intel ha hecho bastantes mejoras a este proceso litográfico, lo cual incluye aspectos como el material de las interconexiones, que pasa a ser cobre con cobalto para eliminar resistencia. Al menos en las capas metálicas cero a cuatro, mientras que las capas de interconexión hasta la catorce son de cobre.

Es un proceso litográfico complejo que usa también patrones múltiples para diversas capas, y un sistema especial de rayos x, estaño y láser, con una longitud de onda de 13.5 nm para aumentar la resolución de los fotolitos usados para crear las capas. Eso también permite aumentar la densidad de los chips, además de una optimización de tiempo y reducción de capas totales necesarias para crear las obleas.

Este chíplet de computación incluye los seis núcleos P (Redwood Cove) de alto rendimiento con otros ocho núcleos E (Crestmont) de alta eficiencia. A pesar de ser una nueva generación, no aportan un aumento en las instrucciones por ciclo (IPC) que ejecutan. Los núcleos Redowood Cove son como los Golden Cove de los actuales Raptor Lake (Core 13.ª generación). Intel sigue insistiendo en que los Meteor Lake se centran en la eficiencia energética y en la nueva arquitectura de chíplets y no en aumentar la potencia. Dicho de otra forma, lo que sí ofrece es más rendimiento en la curva de voltaje. Según Intel, este proceso litográfico aporta un 20 % más de eficiencia energética.

En cuanto a los núcleos E, puesto que toda la arquitectura Meteor Lake es escalable —se pueden crear chíplets con más o menos núcleos u otras características—, se pueden configurar como clústeres de dos o cuatro núcleos. Tienen el doble de caché en general: 64 kB de nivel uno, 4 MB de nivel dos y 3 MB de nivel tres. Esto tendrá un impacto positivo en el rendimiento, porque hay otros cambios de cómo funcionan internamente. Todos los núcleos E y P tienen acceso a las instrucciones AVX10, que es una forma de hacer funcionar las AVX-512 entre los núcleos P y E.

Sistema en chip (SoC)

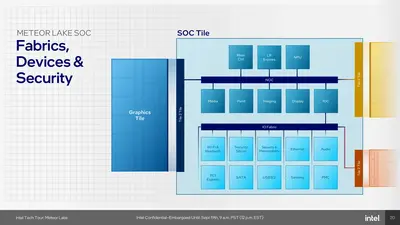

El chíplet del sistema en chip es bastante complejo y se encarga de llevar casi toda la conectividad externa del chips. En ello se incluye las conexiones wifi, Bluetooth, PCIe, SATA, Ethernet o USB, pero también es donde está la gestión de energía, sensores, motor de medios (como el codificador AV1), controlador de pantalla (HDMI 2.1, DisplayPort 2.1)… y dos núcleos E adicionales. A este clúster le ha llamado isla de baja energía. Una isla de energía en un chip son zonas con alimentación y gestión de energía propias.

Las mejoras del planificador de hilos del procesador asignará a estos núcleos E las tareas de menor rendimiento. El ancho de banda de la comunicación de este chíplet se ha aumentado a 128 GB/s a través de una interconexión escalable para las necesidades específicas de cada chip. Este chíplet conecta con los otros tres y con la memoria principal del equipo, por lo que es básicamente el que gestiona realmente el funcionamiento del procesador, incluida la gestión de energía.

Un bloque fundamental de este chíplet de sistema en chip (SoC) es la unidad de procesamiento neuronal (NPU). Es un tipo de unidad que ya se ha visto en los SoC para teléfonos móviles pero que se van a hacer fundamentales en los procesadores de portátiles y sobremesas. AMD ya la incluye en algunos de sus Ryzen.

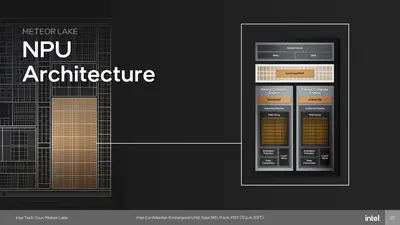

Esta NPU está compuesta por dos motores neuronales que pueden funcionar por separado o juntos, principalmente para inferencias de aprendizaje profundo. Eso sirve por ejemplo para reconocer objetos en imágenes, tras lo cual también podría mejorarlas. Pero el ejemplo dado por Intel, basado en OpenVINO y Audacity, es una canción de funky en la que la NPU es capaz de reconocer la parte cantada y la música y separarlas, creando dos pistas diferentes.

La utilidad de una NPU radica en que es una estructura superespecializada y de muy bajo consumo frente al que tendría hacer lo mismo en los núcleos P y E del procesador. Cosas como reconocimiento de voz, transcripciones de voz a texto y cosas similares se podrán hacer a través de la NPU en Windows y Linux de manera eficiente, por no mencionar los programas de edición de imágenes y vídeo, por ejemplo.

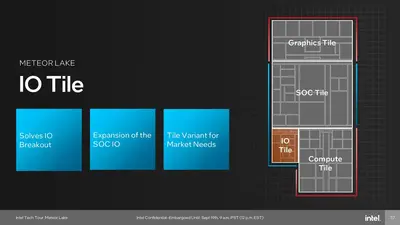

Chíplet de entrada/salida (I/O)

Intel ha querido ser bastante concreto con el funcionamiento del chíplet de entrada/salida porque en realidad, visto lo visto, no sería realmente necesario. Sin embargo, para la compañía resulta no tanto un chíplet para realizar la entrada/salida real del chip, de lo cual se encarga el chíplet de SoC, sino de expandir aún más la conectividad externa del procesador. El nombre elegido por Intel resulta confuso.

Este chíplet de E/S se puede escalar a las necesidades de los procesadores. O sea, que puede proporcionar más o menos conectividad adicional, siendo más o menos pequeño. Este chíplet incluye la conectividad Thunderbolt 4, que no Thunderbolt 5, y las conexiones PCIe 5.0. Con lo cual, para los procesadores de menor coste sin TB4 ni PCIe 5.0, probablemente lo suprima y eso que se ahorra. Un uso adicional para Intel es que el chíplet de sistema en chip solo puede tener conectividad externa por dos de sus lados, por lo que el de E/S aporta más perímetro para ello. Está gobernado por el de SoC, por lo que es una extensión de este.

iGPU

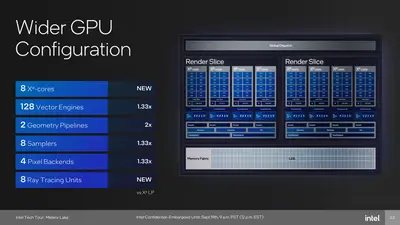

El último chíplet es el que más interesará a muchos, sobre todo por la inclinación jugona de la web. La unidad de procesamiento gráfico (GPU) integrada pasa a ser de arquitectura Xe-LPG, lo cual le dará un buen empujón de rendimiento. La compañía ha optado por incluir ocho núcleos Xe, los cuales se componen de 128 sombreadores cada uno. Eso da 1024 sombreadores en total, que son los mismos que tiene la Arc A380.

Debería ser algo así como una GTX 1650 venida a menos, o más bien como una GT 1630 por el tema de la memoria utilizada, y eso con suerte. Dependerá de la frecuencia turbo que alcance —4 TFLOPS si llegara a 2 GHz, el doble que la Iris Xe—. Tiene acceso a ocho unidades de trazado de rayos, no hay unidades matriciales (XMX) para IA, y hay una serie de cambios que permitirán que tenga el doble de rendimiento por vatio respecto a las iGPU de tipo Iris Xe de 768 sombreadores. No se mencionan otras estructuras relevantes, como las de rasterizado o texturizado.

Vía: AnandTech.