TSMC ha tardado bastante en empezar a dar detalles de su proceso litográfico de 2 nm que supondrá la transición a los transistores de puerta envolvente (GAA). Estos transistores, los cuales se usan en el proceso de 3 nm de Samsung, permiten controlar mejor la energía que los atraviesa haciendo que la puerta envuelva a varios canales apilados. En el caso de TSMC, serán nanoláminas. Pero para controlar la pérdida de energía en su paso por el chip las compañías tienen que cambiar a un sistema de entrega de energía trasera.

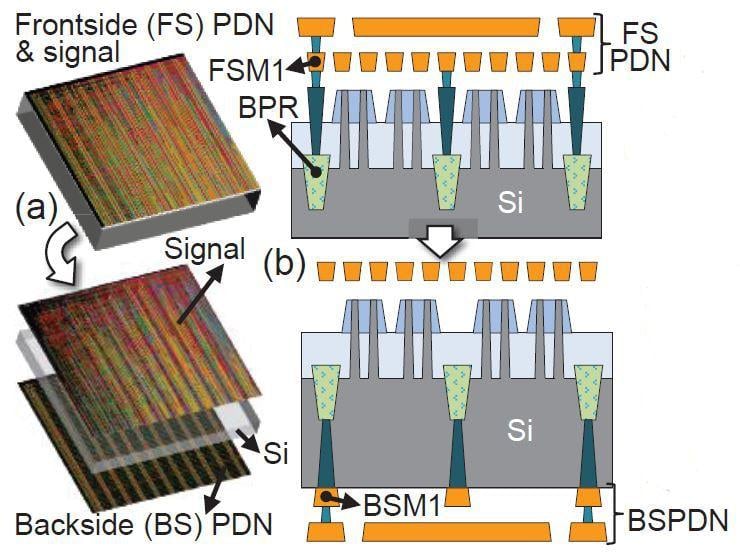

Por cómo se crean los chips, hay una zona a la que se llama frontal de la línea (FEOL), que es la primera que se crea y que son los transistores en sí. Es la que está más cerca de la parte trasera o inferior de la oblea. Luego hay una zona trasera de la línea (BEOL), que es la parte superior o frontal de la oblea, que es la que une el resto de capas en la que venía usándose cobre pero que se ha ido transicionando a otros componentes como el cobalto ya que a medida que las conexiones de cobre se han ido haciendo más pequeñas se ha ido aumentando la resistencia al paso de la corriente. La BEOL es la que conecta directamente con el sustrato sobre el que se deja el chip.

Tradicionalmente se ha hecho que sea la parte superior o frontal de la oblea sea donde resida la gestión de la entrega de energía a los transistores, pero eso hace que la electricidad tenga que pasar por multitud de capas hasta los transistores con la consiguiente resistencia parasitaria, pérdida de energía y creación de inestabilidad dentro de los chips. El paso inevitable a dar con los GAAFET es hacer que la gestión de energía esté en la trasera del chip, que es lo más cercano a donde se tiene que entregar la energía.

Esto lleva a reorganizar el sistema, liberando a su vez espacio en las estructuras que conforman los propios transistores ya que simplemente pasan a tener una línea de señal eliminando la línea de alimentación. Son de esas cosas que resultan obvios sus beneficios pero que hasta que no existía la tecnología para hacerlo ya que se tiene que procesar la trasera de la oblea, eliminando silicio y creando complicadas microvías a través del silicio.

Volviendo al tema de la noticia, el proceso de 2 nm de TSMC va a llegar sin la gestión de energía en la trasera de los chips, lo cual explica por qué el paso de los 3 nm FinFET a los 2 nm GAAFET solo aportan un 10-15 % más de rendimiento a mismo consumo aunque suponga una caída del 25-30 % del consumo a mismo rendimiento. Como he comentado antes, mover la red de entrega de energía a la parte trasera o inferior de la oblea permite mayor integridad de la señal, reduciendo las pérdidas de voltaje por pasar por capas y capas de metal que actúan al final resistencias.

TSMC dejará la gestión de energía en la trasera para una segunda generación del proceso de 2 nm, lo cual por sí solo podría implicar un salto importante de rendimiento mediante frecuencias mayores a mismo consumo. También tendría un impacto directo en la densidad de transistores por milímetro cuadrado, que aumentaría mediante esta forma de alimentarlos al reducir un 20-30 % el tamaño de las estructuras. La reducción de la caída de voltajes estaría en torno al 10 %, que es una reducción más que importante para el buen funcionamiento de los transistores.

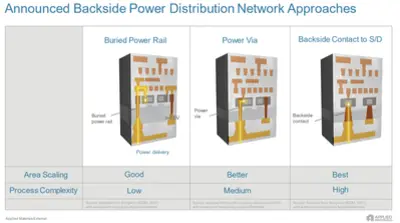

Hay diversas formas de hacer que la entrega de energía esté cerca de los transistores y en el caso de Intel va a usar la más sencilla para tenerlo todo listo para 2024. Es la técnica de los canales de alimentación enterrados, que es de baja complejidad de fabricación y permite un escalado medio. El acercamiento de TSMC será el más complejo pero el que dará los mejores resultados.

Vía: AnandTech, Applied Materials, Imec.