Pat Gelsinger ha apostado por reabrir Intel a terceros en el terreno de la fabricación de chips y eso significa que los potenciales clientes necesitan saber qué procesos tiene planeados la compañía. Por eso era cuestión de tiempo que Intel diera a conocer el calendario de desarrollo de sus procesos y cuándo estarán listos, y eso ha ocurrido en la conferencia Accelerated que ha celebrado esta semana. Ha dado mucha más información de lo que era habitual en la compañía, y este inicipiente aperturismo hecho por Bob Swan y llevado a su máxima expresión por Pat Gelsinger le está sentado muy bien a la compañía.

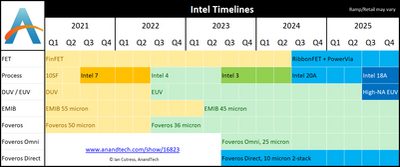

De lo más destacable en la presentación es que la compañía le cambia el nombre a sus procesos litográficos a partir del de 7 nm, pero tampoco hace falta utilizarlo. Bien es cierto que eliminar el símbolo de los nanómetros no molesta —hace mucho tiempo que decir que un proceso de «10 nm» no significa nada de nada porque no es el tamaño del transistor ni de nada del proceso litográfico—, pero Intel ha preferido simplificarlo para llamar a sus procesos 7, 4, 3, 20A y 18A. El calendario dado por Intel está perfectamente recogido en la siguiente imagen de AnandTech.

La compañía ha establecido un calendario muy agresivo de desarrollo, que muchos dudarán de que pueda cumplir porque la cadencia va a ser de un proceso litográfico nuevo hasta 2025. Este año serán los 7 nm —los 10 nm+ y 7 nm fusionados y renombrados para ponerlos en línea con TSMC y Samsung—, el próximo año los 4 nm —los 7 nm renombrados—, en 2023 serán los 3 nm, en 2024 los 20 ángstroms (Å) y en 2025 tocará los 18 Å. Un ángstrom es igual a 0.1 nm, por lo que se entra en una nueva escala litográfica. Eso sí, esto significa que 20 Å son 2 nm y que 18 Å son 1.8 nm, pero es Intel, se cree el nuevo chico guay del barrio. Lo que me extrañaría es que el resto de fundiciones no le copien la nomenclatura en los próximos meses.

El proceso de 7 nm proporcionará un 10-15 % más de rendimiento por vatio frente al de 10 nm SuperFin, y se usa en los Alder Lake de consumo este 2021 y los Sapphire Rapids que llegarán en el primer trimestre de 2022. El proceso de 4 nm será el primero que use luz ultravioleta extrema con un aumento del 20 % del rendimiento por vatio y con mejoras de área. El de 3 nm aumentará un 18 % más el rendimiento por vatio frente al proceso de 4 nm.

También desarrollará nuevas interconexiones a 45 micrones (EMIB) y avanzará en Foveros, su tecnología de apilamiento de chips pasándolo a los 36 mcirones. Pero habrá nuevas versiones llamadas Foveros Omni a 25 micrones y Foveros Direct a 10 micrones, que al final son tecnologías de encapsulado.

Foveros Omni es la tercera generación de esta tecnología y su nombre proviene de ser una conexión omnidireccional lo que permite apilar chips de una manera más heterogénea. El chip superior puede ser más grande que los inferiores, permite conectar chips de una manera cruzada, etc.

Foveros Direct es la cuarta generación y abunda en las mejoras de interconexión permitiendo el soldado directo de conexiones de cobre. Actualmente se utilizan materiales de soldado para conectar las interconexiones como por ejemplo estaño, pero eso implica pérdidas de corriente. En esta generación esos problemas se terminarán.

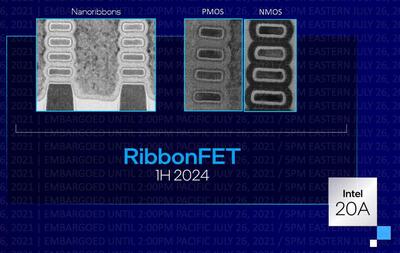

En cuanto al futuro de los transistores, Intel maneja lo que llama transistores de efecto de campo de nanoláminas (RibbonFET), que viene a ser simplemente un GAAFET de toda la vida pero con otro nombre. Samsung los llama MBCFET. Lo habitual es que el canal sean nanotubos apilados y rodeados de un material que hace de puerta, pero si se aumenta la superficie se aumenta el paso de corriente y beneficia a la potencia y eso lleva a Samsung a usar una variante con nanoplanchas. En el caso de Intel lo que hará Intel es usar un sistema similar de nanoplanchas como canal, y los llama láminas como los podría haberlos llamado tablones. El caso es diferenciarse de la competencia.

Por otro lado, la compañía también ha anunciado su tecnología PowerVias, que es el nombre propio de Intel para la tecnología de entrega trasera de energía. Esto permite que la capa más inferior de una oblea no tenga por qué ser la de los transistores. Con PowerVias se pueden crear transistores en mitad de las decenas de capas de que se compone el diseño de un chip, lo que reduce las rutas o vías entre capas hasta los transistores, reduciendo la pérdida de energía y el calor generado.

Un problema viene de que los transistores son la capa más compleja de crear en una oblea, y por tanto si se crea entre medias del total de capas se tarda más en descartar una oblea. El otro es que los transistores se dejan en la capa inferior totalmente opuesta a la capa superior que es la que lleva las conexiones externas para que al darle la vuelta al chip para encapsularlo los transistores, que son lo que más calor suele generar, queden lo más cerca posible de la refrigeración. Al tener los transistores entre medias, no es lo más ideal desde el punto de vista térmico.

Vía: AnandTech.