Hay varias preguntas en el aire sobre la arquitectura Turing que aparentemente quedarán respondidas el 14 de septiembre con la publicación por parte de diversos medios de toda la información sobre ella. En Videocardz han publicado el diagrama de bloques de varias de las unidades de procesamiento gráfico creadas por Nvidia para sus tarjetas gráficas GeForce serie 20, y despeja algunas de esas preguntas.

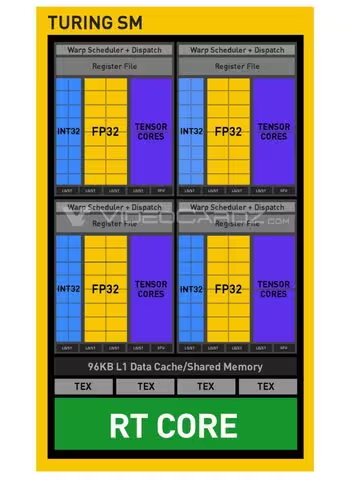

Lo primero que publican es el diagrama del multiprocesador de flujos de datos o SM (simultaneous multithreading) que es la unidad básica con la que se componen las GPU de Nvidia. En ellas, como ya se sabía, se separan los núcleos CUDA en aquellos que ejecutan instrucciones de enteros (INT32) y en coma flotante (FP32) y se añaden los núcleos tensoriales como ocurría en Volta y un núcleo de trazado de rayos que por ahora es una caja negra de la que no dicen de qué se compone.

Nvidia alega un 50 % más de rendimiento por núcleo CUDA con esta separación ya que se pueden ejecutar instrucciones de coma flotante y enteros simultáneamente —por cómo funcionan los SM, se ejecuta la misma operación en todos los núcleos CUDA en lo que se conoce como urdimbres o warps de 32 hilos—, así como un 36 % más de ejecución específica de coma flotante. También ayuda la caché unificada de nivel 1.

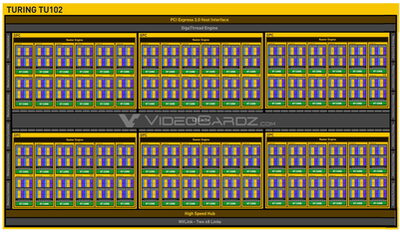

El chip TU102 conforma la RTX 2080 Ti, y como podéis ver tiene doce controladores de memoria, mientras que la RTX 2080 Ti solo tiene 11 GB de memoria. Eso significa que a no mucho tardar llegará una Titan con los doce controladores de memoria activos por un precio superior a los 999 dólares de esta tarjeta gráfica. Tiene un tamaño de 754 mm2.

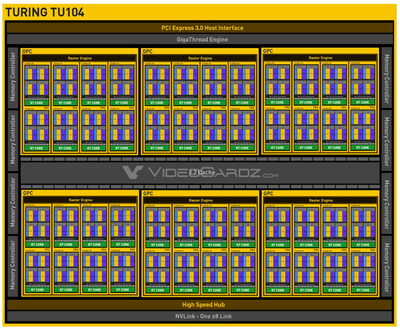

El siguiente diagrama es el del chip TU104 de la RTX 2080, con sus ocho controladores de memoria, y el chip tiene un tamaño de 545 mm2.

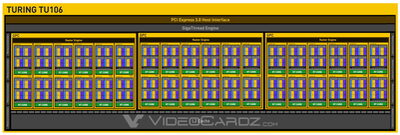

Por último, el chip TU106 que tradicionalmente se usaba para las xx60 será usado ahora por la RTX 2070, por lo que este modelo no usa una versión recortada del chip TU104. Esto abre la puerta a que sea finalmente una «RTX 2060» usando una versión recortada de este chip, el cual tiene un tamaño de 445 mm2.

Videocardz también hace un repaso a otras tecnologías que ha implementado Nvidia en Turing. Por ejemplo, y como he mencionado varias veces, que solo dispongan de 8 GB de VRAM las GeForce RTX significaba que Nvidia habría mejorado la compresión de memoria, y así lo indica. El aumento de ancho de banda efectivo en la arquitectura Turing sería de un 50 % respecto a Pascal, por lo que se hace más con menos memoria. Se utiliza para ello un algoritmo de compresión sin pérdidas, por lo que la falta de mejora en el apartado de ancho de banda físico pudiera ser criticado, pero lo que importa es el ancho de banda efectivo.

Nvidia implementa en esta arquitectura nuevas técnicas de sombreado, como un sombreado en malla para mejorar el sombreado por teselización, vertelizado y geometrizado, se confiere al desarrollador un control de sombreado variable para eliminarlo en zonas donde no aporta una mejora visual, se guarda en memoria las texturas creadas para no crear duplicados en ella para distintos procesos, y mejoras para la creación de gráficos para realidad virtual.

La arquitectura Turing permite a las tarjetas gráficas mover dos paneles de 8K a 60 Hz a través del conector DisplayPort, o el USB tipo C que tienen las tarjetas gráficas y que usa también DisplayPort. Pueden codificar a HEVC a 8K y 30 FPS, y decodificar vídeo a 8K con hasta el códec VP9 10/12 con HDR. Por último, según lo indicado por Videocardz, la conexión NVLink en el TU102 es de dos canales ×8, mientras que en el TU104 solo se dispone de uno. A pesar de que no alcanzarán los 300 GB/s de las tarjetas gráficas profesionales Quadro, la comunicación entre dos tarjetas gráficas GeForce RTX será muy superior al del actual conector de SLI. El TU106 no cuenta con NVLink.

Vía: Videocardz.