ARM presentó en septiembre del año pasado las plataformas Neoverse V1 y Neoverse N2 para inteligencia artificial, y ha aprovechado la reciente presentación de ARMv9 para dar más detalles de ambas plataformas. Tenéis un artículo completo en AnandTech entrando a detallar los cambios de la arquitectura en base a la información nueva; me voy a centrar en la información más general dada por la compañía en su web, que es más fácil de digerir.

Neoverse V1 es la arquitectura para computación de alto rendimiento y por tanto la que le faltaba a ARM en su catálogo. Esta arquitectura aporta un 50 % más de instrucciones por ciclo que la arquitectura Neoverse N1. Una de las ventajas es la inclusión de extensiones para vectores escalable (SVE) orientadas al cómputo de alto rendimiento y aprendizaje profundo, además de cálculos bfloat16 (coma flotante neuronal). De hecho es en SVE en lo que más se para la compañía ya que permite aumentar enormemente el rendimiento en cierto cálculos, y es para lo que está diseñada.

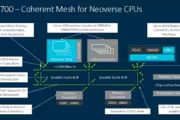

La interconexión escalable usada para estos procesadores será la CMN-700, que permite comunicar con memoria variada (DDR5, HBM2e, HBM3), otros controladores de E/S, 128 canales PCIe 5.0 (CCIX/CXL), y comunicación externa con otros procesadores. Es una interconexión coherente, que es lo habitual para sincronizar la información entre procesadores ejecutando código sobre un mismo conjunto de datos.

En cuanto a Neoverse N2, en este caso aporta un 40 % más de rendimiento que su predecesor, pero en este caso está orientado a sistemas en la frontera de las redes. Está basado en la arquitectura ARMv9 y basado en SVE2. La idea detrás de esta arquitectura es la de tener una alta eficiencia energética y reducción del tamaño de los procesadores manteniendo un buen rendimiento. Pero también que sea altamente escalable, pudiendo ir de los 32 núcleos a los 192 núcleos.

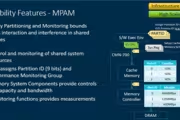

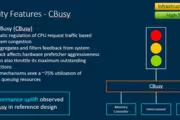

Al igual que el Neoverse V1, incluye un sistema de partición y monitorización de memoria (MPAM) para poder distribuir y controlar adecuadamente el acceso a los recursos del sistema al nivel de proceso. También incluye CBusy, un regulador de las solicitudes a la CPU manteniendo adecuadamente una cola en el acceso a los recursos que, según la compañía, permite un 15 % más de rendimiento en ciertas situaciones.

Es también una plataforma más segura, con todo lo necesario para las comunicaciones de estaciones base 5G, pero también en el terreno de la seguridad de la memoria y otros aspectos de los procesadores que usen Neoverse N2. Está pensado para diseño a 5 nm. La compañía también habla de mejoras en la ejecución de Nginx, por ejemplo, de hasta un 30 % respecto a N1, y de un 20 % más de procesamiento de paquetes con DPDK.