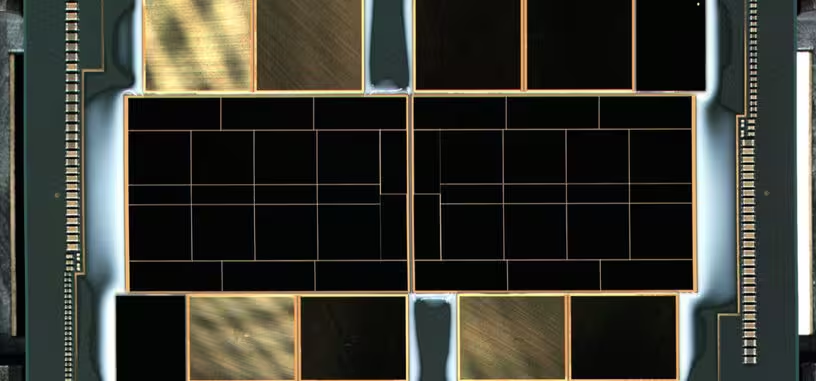

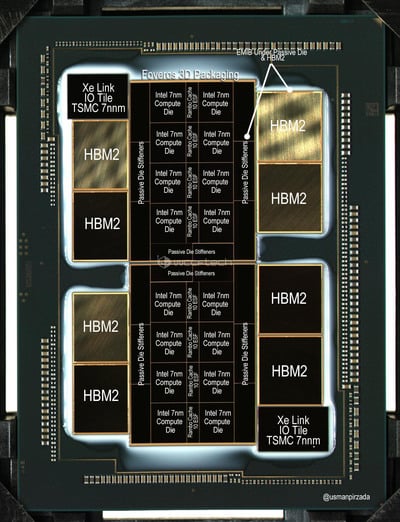

Raja Koduri mostró una GPU Xe-HPC compuesta de dos estructuras de computación y parece más un puzle que un procesador. Ahora desde WCCFTech han arrojado un poco más de luz con una imagen anotada en el que indica qué es qué así como el proceso de fabricación de cada elemento. Hay mucha tecnología de ensamblado y empaquetado en este procesador, lo cual hay que leerlo como «de alto coste», por lo que no sería viable en procesadores de consumo.

El chip principal de cada estructura está compuesto por veinte pastillas de las cuales ocho son refuerzos pasivos para lo que tienen debajo que no es otra cosa que los EMIB (puentes de interconexión multichip), que es básicamente el intermediador. Intel debería usar ODI (interconexión omnidireccional) como interconexión en sí. Este chip está creado con la tecnología de empaquetado Foveros —apilamiento de varios chips—. EMIB viene ser un intermediador de pequeño tamaño en lugar de tener que usar el sustrato inferior o una capa más amplia para comunicar varias pastillas.

Los ocho cuadrados del chip principal es una pastilla de cómputo fabricada con el proceso de 7 nm de Intel. Entre ellas se encuentran cuatro pastillas que son la caché Rambo —no es el nombre comercial sino el interno que usa Intel— fabricado con el proceso de 10 nm SuperFin+ de Intel. A los lados en cada estructura se ven cuatro chips de HBM2 —del fabricante que sea y con la litografía que sea— interconectadas mediante EMIB, y también se ve la pastilla de E/S que está fabricada a 7 nm por TSMC. Así que sí, cada estructura son al menos veinte pastillas de distintos fabricantes y procesos litográficos. Es una buena obra de ingeniería que es solo el avance de lo que pueden ser los procesadores de Intel en el futuro cercano.

Vía: WCCFTech.