AMD se ha adelantado a su evento del CES 2017 dando bastantes más detalles de la arquitectura Vega con la que creará su nueva generación de tarjetas gráficas. No ha dado modelos concretos que la vayan a implementar ni su potencia, aunque competirán previsiblemente en la gama alta y entusiasta, y quizás se deslice algún que otro chip a portátiles y todo en uno.

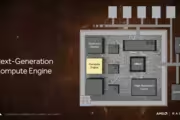

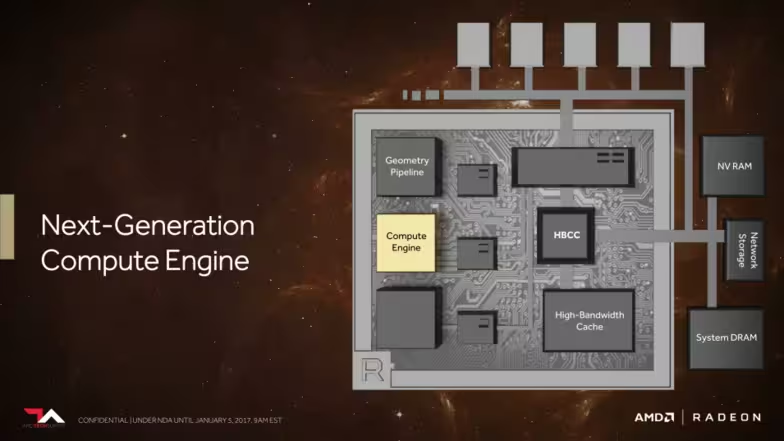

Puesto que se trata de un vistazo preliminar a la arquitectura, todavía faltan unos meses para que lleguen las tarjetas gráficas. Según los rumores, eso sería en torno a marzo o abril. Pero de momento es un buen aperitivo saber que AMD prescinde en Vega de la arquitectura GCN y la sustituye por NCU —unidad de cómputo de nueva generación, o next-generación compute unit—.

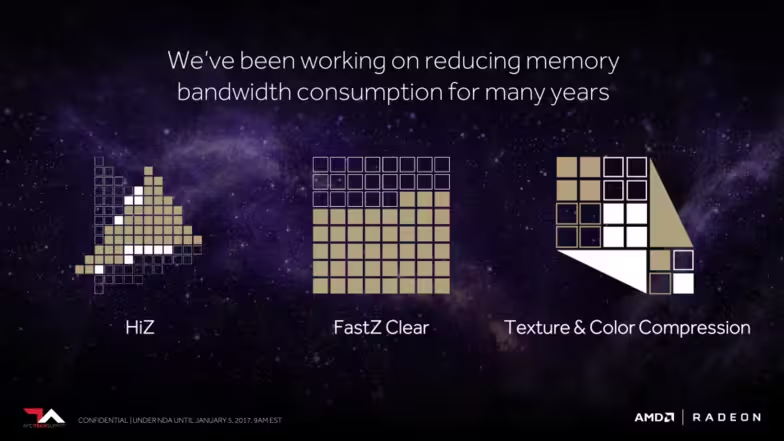

Esto implica una enorme cantidad de cambios internos destinados a mejorar aspectos fundamentales de una tarjeta gráfica en los que AMD siempre ha fallado, como son el uso de la memoria y el ancho de banda. Pero también posibilita aspectos de computación como por ejemplo que en cada sombreador —una unidad aritmético lógico o ALU— se pueden ejecutar dos operaciones en coma flotante en precisión simple (FP16) por ciclo de reloj en vez de una sola de doble precisión (FP32), lo que permitirá aprovechar más la potencia de cada sombreador.

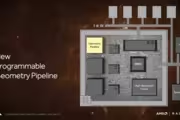

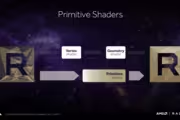

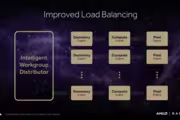

Cada unidad de cómputo (CU) sigue compuesta por 64 sombreadores, y se podrá distribuir la carga de trabajo entre más de cuatro SE —motores de sombreado o shader engine, la unidad que engloba varias CU—. El aprovechamiento de los recursos ha sido el talón de Aquiles de AMD durante años, y con este cambio también acerca su arquitectura a como lo hace Nvidia. También se mejora los motores de geometría para ejecutar más polígonos por ciclo.

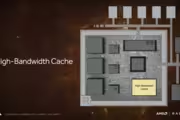

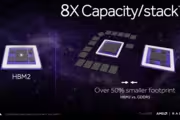

La memoria HBM2 también es un aspecto fundamental de esta nueva arquitectura, ya que puede funcionar hasta a 2 GHz de manera efectiva, aunque Samsung también produce los chips HBM2 a 1.6 GHz. Esto da un ancho de banda máximo de 1 TB/s, frente a los 480 GB/s de la Titan X. Con los cambios de aprovechamiento de la arquitectura, puede significar una mejora sustancial de potencia por parte de AMD. Este tipo de memoria también es altamente escalable, para poder combinarla como cada chip en especial necesite.

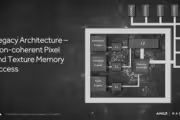

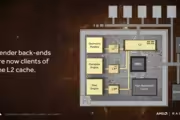

Hay cambios en el proceso de rasterización de polígonos, ya que usarán directamente la caché de nivel 2 (L2) en vez de tener que hacerlo a través del controlador de memoria. Esto sigue recayendo en la mejora de los puntos grises de las arquitecturas previas de AMD, y permite la selección de los niveles de iluminación de las texturas aplicadas a los polígonos de una manera más rápida y eficiente.

Por lo demás, son cambios profundos en la arquitectura, pero que hasta el segundo trimestre no lleguen al mercado.