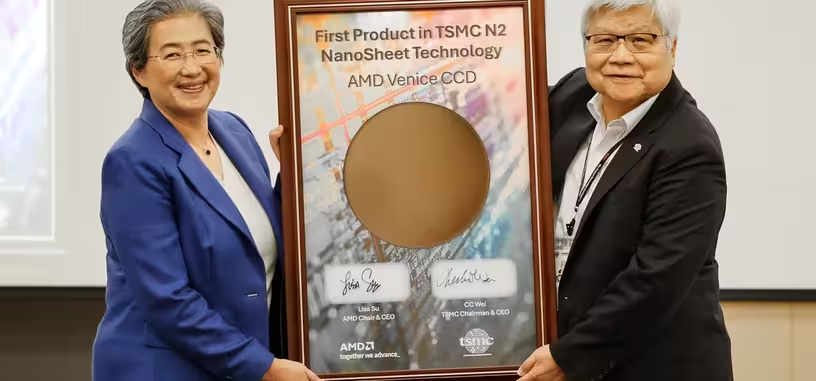

Los diseñadores de chips han pasado de puntillas por el proceso de 3 nm de TSMC porque no proporcionaba una gran diferencia respecto a los de 4 nm como para justificar el importante aumento de precio. Han estado esperando al de 2 nm, que ya está siendo usado en producción en masa, y que ahora AMD ha confirmado que lo va a usar para el chíplet de cómputo de los procesadores Venice, los EPYC basados en la arquitectura Zen 6 que llegarán a los centros de datos el próximo año.

Como dice AMD, es el primer producto de cómputo de alto rendimiento que usa este proceso litográfico en salir a fotolitos, que es la fase que da por finalizado el diseño y las pruebas del chip. Esos fotolitos se usan para la producción en masa, aunque antes TSMC tendrá que hacer la producción de prueba antes de alcanzar la producción en masa. Ese proceso ser medio año, así que a principios del año que viene podrían estar ya en los centros de datos.

Además, AMD va a usar la fábrica de Arizona de TSMC para producir este diseño a 2 nm, que es una demostración que ya no hay ningún veto por parte del gobierno taiwanés para que la compañía produzca con su proceso más puntero fuera del país.