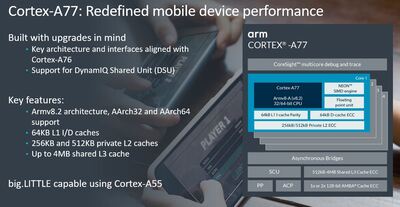

La inglesa ARM ha anunciado un nuevo núcleo que conformará los procesadores para dispositivos móviles que llegarán en los próximos meses. Se trata del Cortex-A77, y es la tercera generación del diseño DynamIQ cuyo predecesor es el Cortex-A76. Según la compañía, supone una mejora de rendimiento del 20 % de las IPC (instrucciones por ciclo) respecto al anterior, manteniendo el proceso de fabricación a 7 nm y misma frecuencia de 3 GHz en la comparación.

Hay un apartado que la compañía no ha mencionado como es el del consumo, y parece que no va a haber mejorado en este terreno, o incluso podría aumentar ligerísimamente a cambio de esa mejora de rendimiento. «Misma duración de varios días pero con más potencia», dice ARM. En cómputo en coma flotante los cambios permiten una mejora del 35 % y un 15 % más de ancho de banda, y en enteros mejora un 20 %.

Los cambios para ese aumento del 20 % de las IPC se centran en que implementa la versión de núcleo ARMv8.2, los sets de instrucciones AArch32 y AArch64, mejoran la caché N1 (nivel 1) de instrucciones y datos a los 64 KB, hay caché de N2 privadas de 256 y 512 KB, y permite hasta 4 MB de caché de N3. La mejora de la caché supone la mayor parte de la mejora de rendimiento.

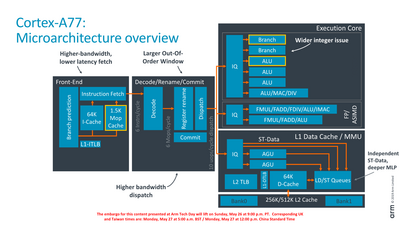

También mejoran el predictor de saltos usado en la ejecución fuera de orden para evitar los fallos de predicción, aumentando un 50 % el ancho de banda del predictor y usando hasta seis instrucciones por ciclo para ello, y mejora un 25 % la ventana de trabajo fuera de orden hasta las 160 instrucciones.

Esta ejecución fuera de orden es predecir instrucciones que podrían no requerir de resultados de otras instrucciones previas y por tanto ejecutarse de manera adelantada, pero no siempre predice lo bien. Se hace para usar momentos en los que el procesador estaría sin hacer nada mientras a la espera de que las instrucciones previas acaben de ejecutarse.

Vía: AnandTech.